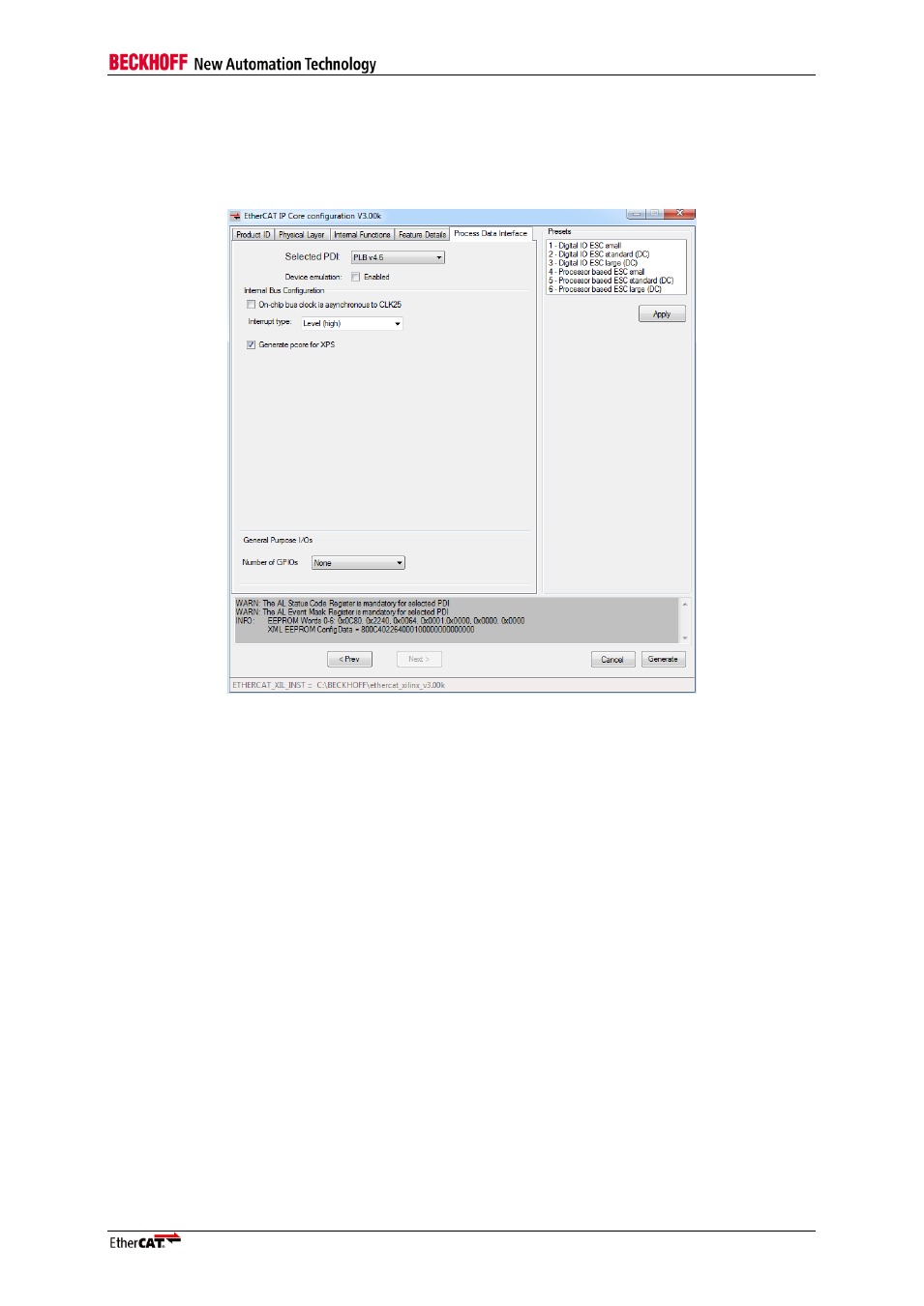

5 processor local bus (plb) configuration, Figure 22: register pdi, Plb interface configuration – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v3.00k User Manual

Page 59

IP Core Configuration

Slave Controller

– IP Core for Xilinx FPGAs

III-47

5.1.5.5

Processor Local Bus (PLB) Configuration

The PLB v4.6 PDI connects the IP Core with a PLB Master (e.g. Xilinx MicroBlaze

TM

). The data bus

with is 32 bit, and the address bus is also 32 bit wide.

Figure 22: Register PDI

– PLB Interface Configuration

Device emulation

Enable Device emulation (0x0141[0]=1). This feature should be disabled in most use cases.

On-Chip Bus CLK is asynchronous to CLK25 core clock

Enable if the On-chip BUS CLK is asynchronous to CLK25. Additional synchronization stages are

added in this case.

Interrupt type

Select the usage type of the interrupt signal (level or edge). Since the main interrupt can have different

sources, a level based interrupt is typically required.

Generate pcore for XPS

Enable generation of an EtherCAT IP Core package for Xilinx XPS/EDK, i.e., a pcores folder structure

with source files and module definitions.