Basler Electric BE1-11 Modbus Protocol User Manual

Page 33

9424200774 Rev B

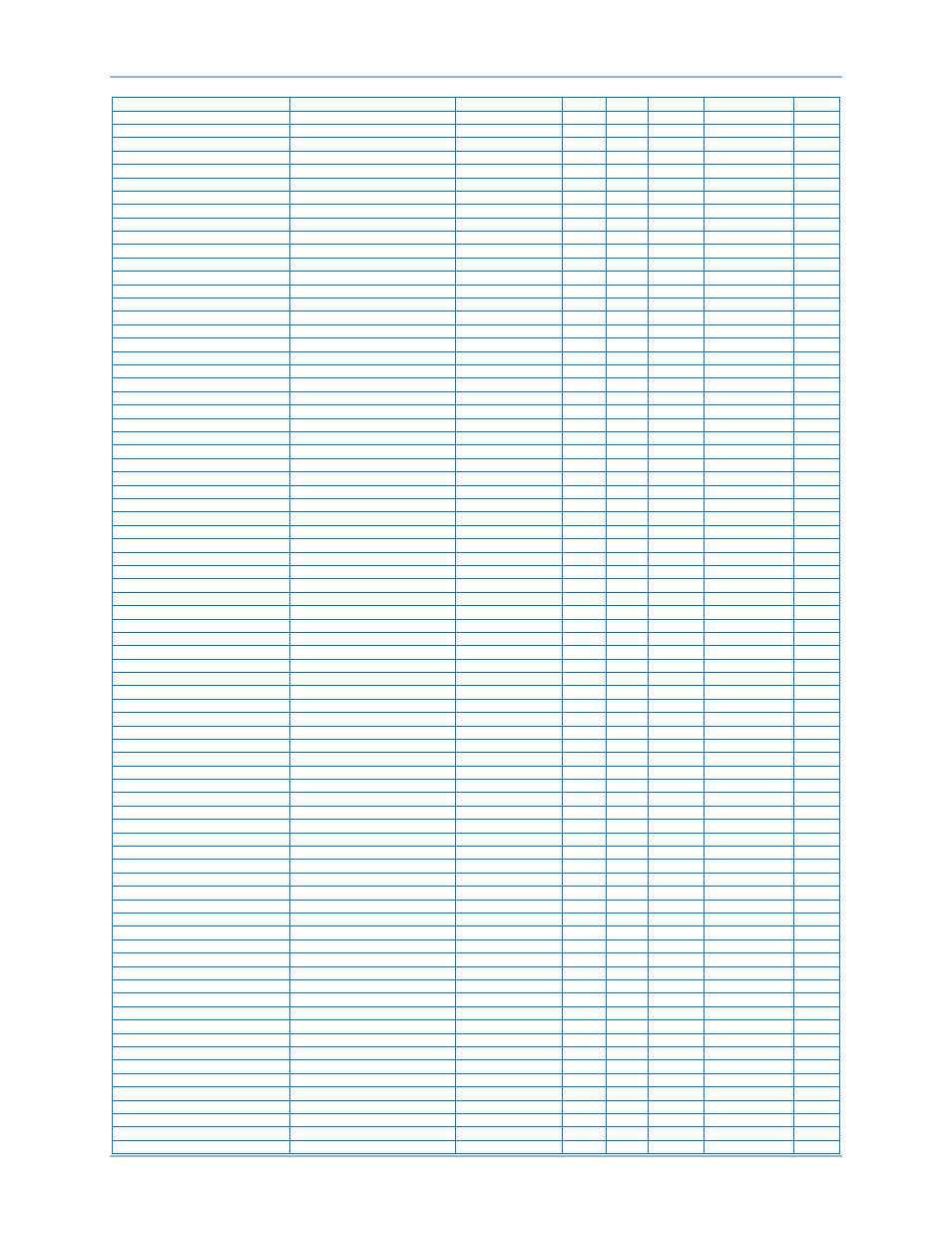

27

BE1-11

Register Table

Name

Description

Register

Type

Bytes Writable

Range

Style

50-5

Target Unbalance

959 bit 6

Uint16 2

R

True=1 False=0

FGIMT

50-5

67 Target Unbalance

959 bit 7

Uint16 2

R

True=1 False=0

FGIT

50-6

Target Unbalance

959 bit 8

Uint16 2

R

True=1 False=0

FGIMT

50-6

67 Target Unbalance

959 bit 9

Uint16 2

R

True=1 False=0

FGIT

Reserved

959 bit 10-963 bit 2

51-1

Target Unbalance

963 bit 3

Uint16 2

R

True=1 False=0

FGIMT

51-1

67 Target Unbalance

963 bit 4

Uint16 2

R

True=1 False=0

FGIT

51-2

Target Unbalance

963 bit 5

Uint16 2

R

True=1 False=0

FGIMT

51-2

67 Target Unbalance

963 bit 6

Uint16 2

R

True=1 False=0

FGIT

51-3

Target Unbalance

963 bit 7

Uint16 2

R

True=1 False=0

FGIMT

51-3

67 Target Unbalance

963 bit 8

Uint16 2

R

True=1 False=0

FGIT

51-4

Target Unbalance

963 bit 9

Uint16 2

R

True=1 False=0

FGIMT

51-4

67 Target Unbalance

963 bit 10

Uint16 2

R

True=1 False=0

FGIT

51-5

Target Unbalance

963 bit 11

Uint16 2

R

True=1 False=0

FGIMT

51-5

67 Target Unbalance

963 bit 12

Uint16 2

R

True=1 False=0

FGIT

51-6

Target Unbalance

963 bit 13

Uint16 2

R

True=1 False=0

FGIT

51-6

67 Target Unbalance

963 bit 14

Uint16 2

R

True=1 False=0

FGIT

51-7

Target Unbalance

963 bit 15

Uint16 2

R

True=1 False=0

FGIT

51-7

67 Target Unbalance

964 bit 0

Uint16 2

R

True=1 False=0

FGIT

51-8

Block

964 bit 1

Uint16 2

R

True=1 False=0

T

51-8

Pickup

964 bit 2

Uint16 2

R

True=1 False=0

T

51-8

Trip

964 bit 3

Uint16 2

R

True=1 False=0

T

51-8

Target A

964 bit 4

Uint16 2

R

True=1 False=0

T

51-8

Target B

964 bit 5

Uint16 2

R

True=1 False=0

T

51-8

Target C

964 bit 6

Uint16 2

R

True=1 False=0

T

51-8

Target Negative Sequence

964 bit 7

Uint16 2

R

True=1 False=0

T

51-8

Target Residual

964 bit 8

Uint16 2

R

True=1 False=0

T

51-8

Target Independent Ground

964 bit 9

Uint16 2

R

True=1 False=0

T

51-8

67 Target A

964 bit 10

Uint16 2

R

True=1 False=0

T

51-8

67 Target B

964 bit 11

Uint16 2

R

True=1 False=0

T

51-8

67 Target C

964 bit 12

Uint16 2

R

True=1 False=0

T

51-8

67 Target Negative Sequence

964 bit 13

Uint16 2

R

True=1 False=0

T

51-8

67 Target Residual

964 bit 14

Uint16 2

R

True=1 False=0

T

51-8

67 Target Independent Ground

964 bit 15

Uint16 2

R

True=1 False=0

T

51-8

Target Positive Sequence

965 bit 0

Uint16 2

R

True=1 False=0

T

51-8

67 Target Positive Sequence

965 bit 1

Uint16 2

R

True=1 False=0

T

51-8

Target Unbalance

965 bit 2

Uint16 2

R

True=1 False=0

T

51-8

67 Target Unbalance

965 bit 3

Uint16 2

R

True=1 False=0

T

51-9

Block

965 bit 4

Uint16 2

R

True=1 False=0

T

51-9

Pickup

965 bit 5

Uint16 2

R

True=1 False=0

T

51-9

Trip

965 bit 6

Uint16 2

R

True=1 False=0

T

51-9

Target A

965 bit 7

Uint16 2

R

True=1 False=0

T

51-9

Target B

965 bit 8

Uint16 2

R

True=1 False=0

T

51-9

Target C

965 bit 9

Uint16 2

R

True=1 False=0

T

51-9

Target Negative Sequence

965 bit 10

Uint16 2

R

True=1 False=0

T

51-9

Target Residual

965 bit 11

Uint16 2

R

True=1 False=0

T

51-9

Target Independent Ground

965 bit 12

Uint16 2

R

True=1 False=0

T

51-9

67 Target A

965 bit 13

Uint16 2

R

True=1 False=0

T

51-9

67 Target B

965 bit 14

Uint16 2

R

True=1 False=0

T

51-9

67 Target C

965 bit 15

Uint16 2

R

True=1 False=0

T

51-9

67 Target Negative Sequence

966 bit 0

Uint16 2

R

True=1 False=0

T

51-9

67 Target Residual

966 bit 1

Uint16 2

R

True=1 False=0

T

51-9

67 Target Independent Ground

966 bit 2

Uint16 2

R

True=1 False=0

T

51-9

Target Positive Sequence

966 bit 3

Uint16 2

R

True=1 False=0

T

51-9

67 Target Positive Sequence

966 bit 4

Uint16 2

R

True=1 False=0

T

51-9

Target Unbalance

966 bit 5

Uint16 2

R

True=1 False=0

T

51-9

67 Target Unbalance

966 bit 6

Uint16 2

R

True=1 False=0

T

87

Unrestrained Trip

966 bit 7

Uint16 2

R

True=1 False=0

GMT

Reserved

966 bit 8

Uint16 2

R

True=1 False=0

GMT

87

Alarm A

966 bit 9

Uint16 2

R

True=1 False=0

GMT

87

Alarm B

966 bit 10

Uint16 2

R

True=1 False=0

GMT

87

Alarm C

966 bit 11

Uint16 2

R

True=1 False=0

GMT

87

Unrestrained Target A

966 bit 12

Uint16 2

R

True=1 False=0

GMT

87

Unrestrained Target B

966 bit 13

Uint16 2

R

True=1 False=0

GMT

87

Unrestrained Target C

966 bit 14

Uint16 2

R

True=1 False=0

GMT

87

2nd Harmonic Inhibit

966 bit 15

Uint16 2

R

True=1 False=0

GT

87

5th Harmonic Inhibit

967 bit 0

Uint16 2

R

True=1 False=0

GT

55

Block

967 bit 1

Uint16 2

R

True=1 False=0

M

55

Pickup

967 bit 2

Uint16 2

R

True=1 False=0

M

55

Trip

967 bit 3

Uint16 2

R

True=1 False=0

M

55

Target

967 bit 4

Uint16 2

R

True=1 False=0

M

21-1

Block

967 bit 5

Uint16 2

R

True=1 False=0

G

21-1

Pickup

967 bit 6

Uint16 2

R

True=1 False=0

G

21-1

Trip

967 bit 7

Uint16 2

R

True=1 False=0

G

21-1

Target AB

967 bit 8

Uint16 2

R

True=1 False=0

G

21-1

Target BC

967 bit 9

Uint16 2

R

True=1 False=0

G

21-1

Target CA

967 bit 10

Uint16 2

R

True=1 False=0

G

21-2

Block

967 bit 11

Uint16 2

R

True=1 False=0

G