Appendix b. ports & parameters, Input ports – Altera Stratix GX Transceiver User Manual

Page 297

Altera Corporation

B–1

January 2005

Appendix B. Ports &

Parameters

Input Ports

lists the input ports of the Stratix

®

GX device.

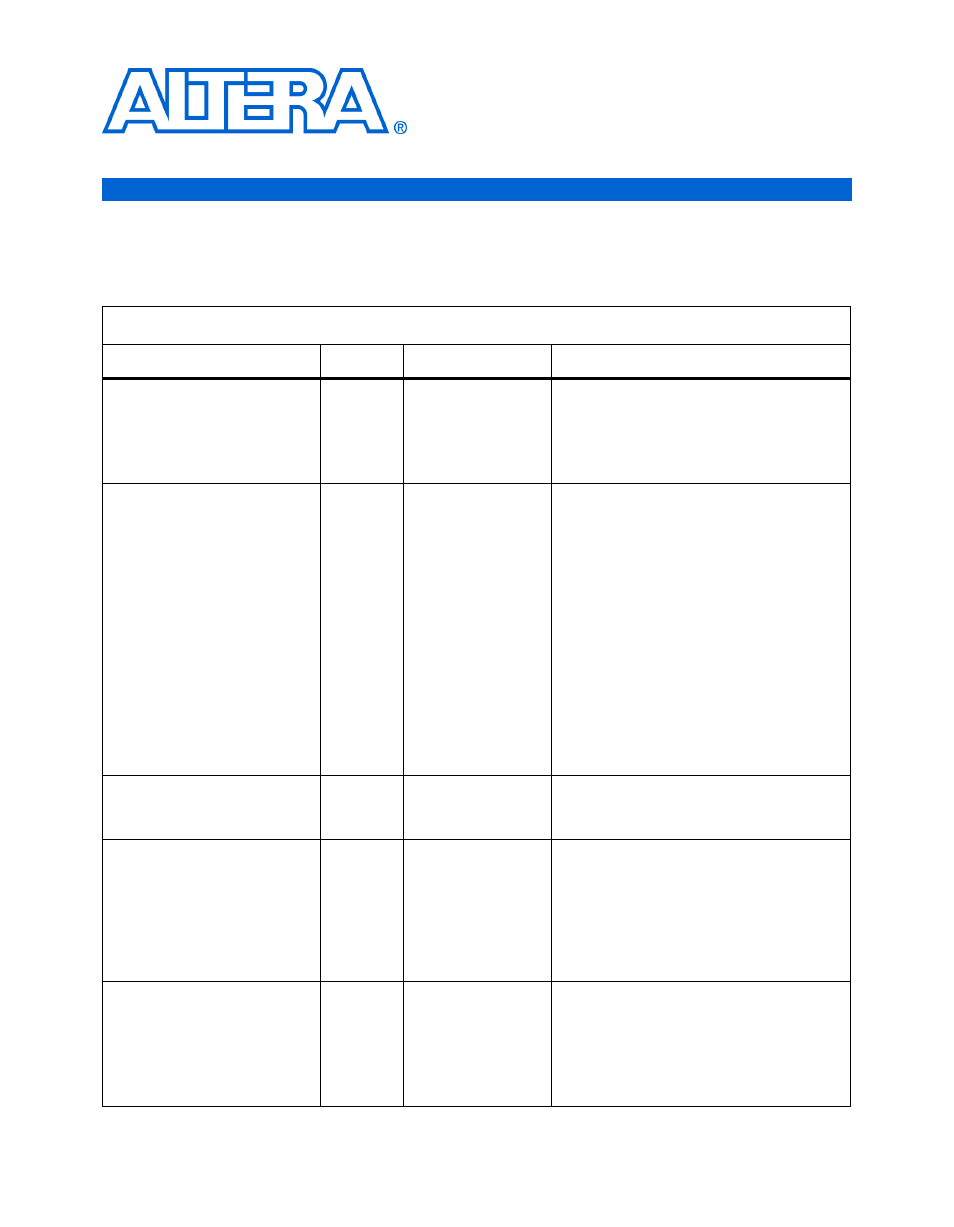

Table B–1. Input Ports (Part 1 of 4)

Port Name

Required

Description

Comments

inclk[]

See

comments

Transceiver block

transmitter PLL

reference input

clock.

Input port [NUMBER_OF_QUADS - 1..0]

wide. If you use the transmitter PLL, the

inclk[]

port is required. If you set the

OPERATION_MODE

parameter to

TX

or

DUPLEX

, the

inclk[]

port is required.

pll_areset[]

No

Asynchronous reset

for the transceiver

block transmitter

PLL. This signal

powers down the

entire transceiver

block. When placing

refclkb pins, see

Appendix C,

REFCLKB Pin

Constraints

for

information about

analog reads and

refclkb pin usage

constraints.

Input port [NUMBER_OF_QUADS - 1..0]

wide.

rx_in[]

Yes

Transceiver block

receiver channel

data input port.

Input port [NUMBER_OF_CHANNELS -

1..0] wide.

rx_cruclk[]

No

Clock recovery unit

(CRU) for the

transceiver block

receiver PLL

reference input

clock.

Input port [NUMBER_OF_QUADS - 1..0]

wide. When you set the

OPERATION_MODE

parameter to

TX

or

DUPLEX

, the

rx_cruclk[]

port cannot

be used. If you use this parameter, the

transceiver block transmitter PLL cannot be

instantiated.

rx_bitslip[]

No

Controls bit slipping

circuitry in the word

aligner.

Input port [NUMBER_OF_CHANNELS -

1..0] wide. If you enable the

rx_bitslip

port, the

rx_enacdet[]

port cannot be

connected and the

USE_AUTO_BIT_SLIP

parameter must

be set to

OFF

.