Altera External Memory PHY Interface User Manual

Page 74

4–6

Chapter 4: Support for Arria GX, HardCopy II, Stratix II, and Stratix II GX Devices

DDR2/DDR SDRAM

External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide

© January 2010

Altera Corporation

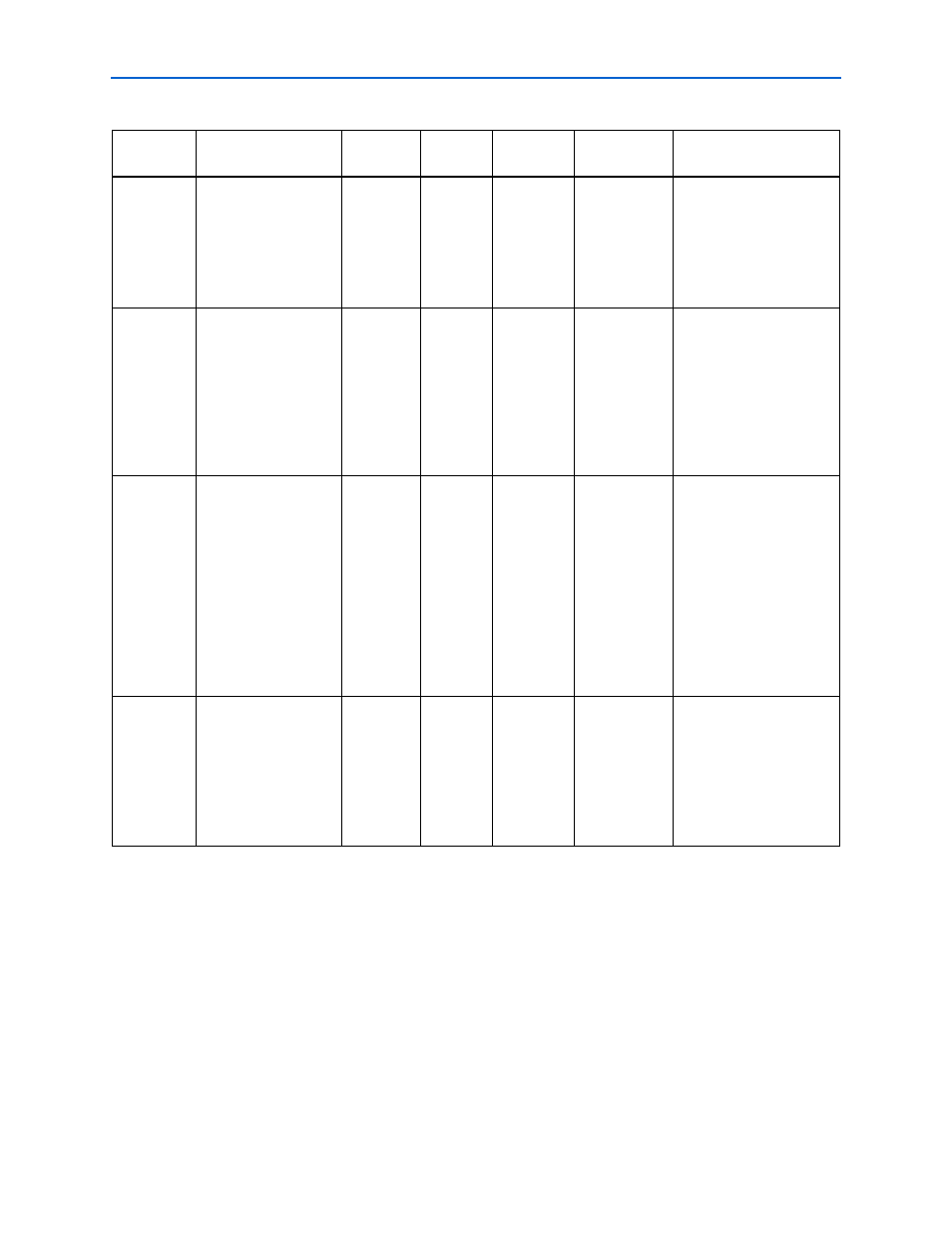

PLL Reconfiguration

The ALTMEMPHY MegaWizard interface automatically generates the PLL

reconfiguration block by instantiating an ALTPLL_RECONFIG variation for Stratix II

and Stratix II GX devices to match the generated ALTPLL megafunction instance. The

ALTPLL_RECONFIG megafunction varies the resynchronization clock phase and the

measure clock phase.

Half-rate

and full rate

mem_clk_ext_2x

C3

> 0

Full-Rate

Dedicated

This clock is only used if

the memory clock

generation uses dedicated

output pins. Applicable

only in HardCopy II or

Stratix II prototyping for

HardCopy II designs.

Half-rate

and full rate

resync_clk_2x

C4

Calibrated

Full-Rate

Regional

Clocks the

resynchronization

registers after the capture

registers. Its phase is

adjusted to the center of

the data valid window

across all the

DQS-clocked DDIO

groups.

Half-rate

and full rate

measure_clk_2x

C5

Calibrated

Full-Rate

Regional

This clock is for VT

tracking. This free-running

clock measures relative

phase shifts between the

internal clock(s) and those

being fed back through a

mimic path. As a result,

the ALTMEMPHY

megafunction can track

VT effects on the FPGA

and compensate for the

effects.

Half-rate

and full rate

ac_clk_2x

—

0,

90

,180,

270

Full-Rate

Global

The ac_clk_2x clock is

derived from either

mem_clk_2x

(when you

choose 0

or 180 phase

shift) or

write_clk_2x

(when

you choose 90

or 270

phase shift).

Notes to

(1) In full-rate designs a _1x clock may run at full-rate clock rate.

(2) This clock should be of the same clock network clock as the resync_clk_2x clock.

Table 4–1. DDR2/DDR SDRAM Clocking in Arria GX, HardCopy II, Stratix II, and Stratix II GX Devices (Part 2 of 2)

Design

Rate

Clock Name

Postscale

Counter

Phase

(Degrees)

Clock Rate

Clock

Network Type

Notes