Note 1) – Altera External Memory PHY Interface User Manual

Page 35

Chapter 3: Functional Description—ALTMEMPHY (nonAFI)

3–19

ALTMEMPHY Signals

© January 2010

Altera Corporation

External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide

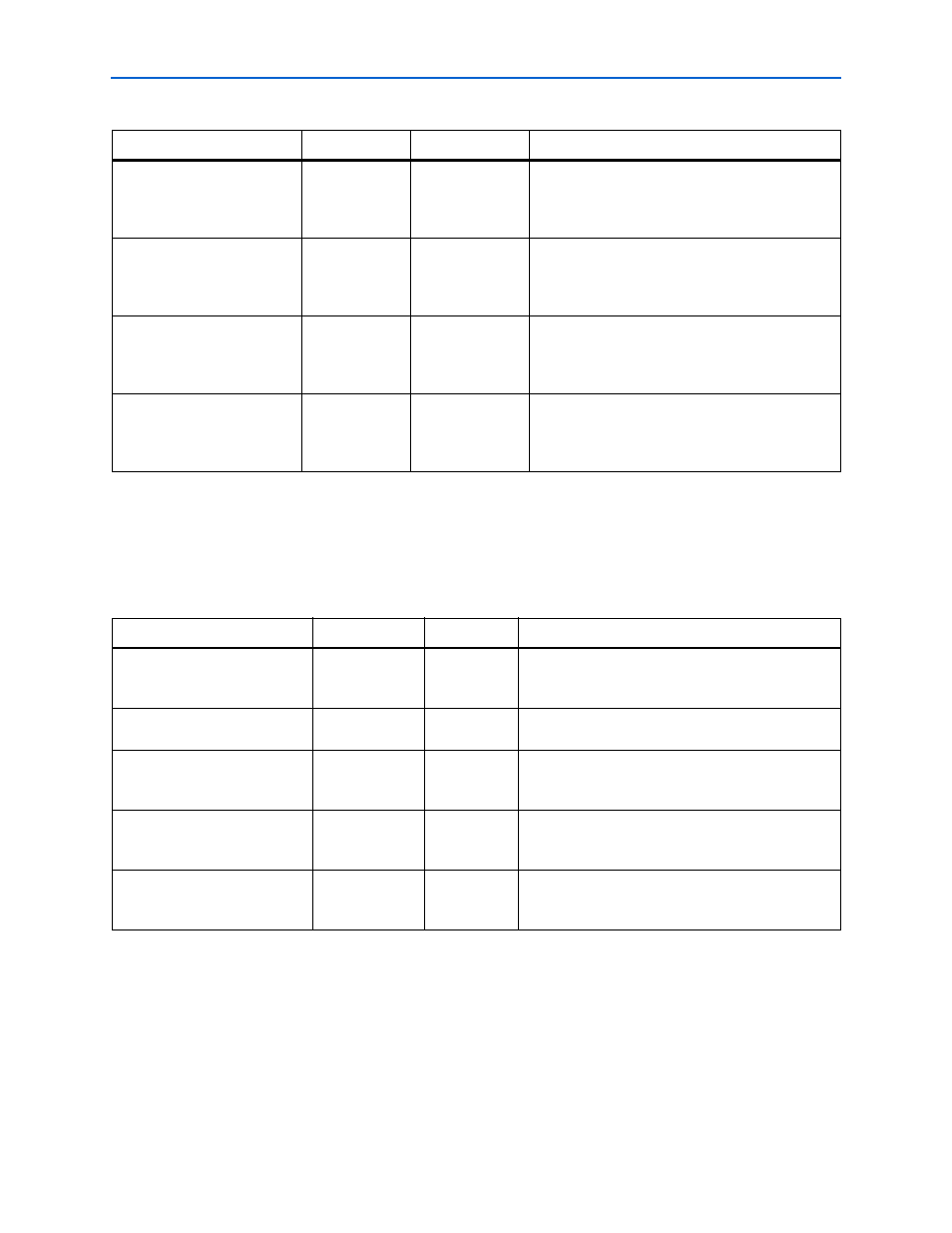

ctl_mem_wdata

input

MEM_IF_

DWIDTH×

DWIDTH_

RATIO

The write data bus, which has valid data in the same

clock cycles that control_wdata_valid is

asserted, see

Read Commands and Read Data” on page 3–47

ctl_mem_wdata_valid

input

1

Generates the mem_dq output enable. When

asserted, the ctl_mem_rdata_valid signal

indicates that the coincident read data on

ctl_mem_rdata

is valid.

ctl_mem_we_n_h

input

1

The write-enable signal from the controller to the

memory. Output during the high half-period of the

address and command clock and driven by the

memory controller.

ctl_mem_we_n_l

input

1

The write-enable signal from the controller to the

memory. Output during the low half-period of the

address and command clock and driven by the

memory controller.

Note to

(1) The “_h” and “_l” stand for high and low. They signify in which half of the clock cycle the data is output. The _h data is output when the

corresponding clock, for example ac_clk_2x, is high. The _l data is output when the ac_clk_2x clock is low. The signals with _h and

_l

allow you to select between 1T and 2T addressing. For half-rate designs, 1T is where the address and command signals are driven for one

clock; 2T is where they are driven for 2 clocks. For full-rate designs, ensure the same signal drives both _h and _l signals and 2T addressing

is used. Also when high-performance controllers use ALTMEMPHY, 2T addressing is used.

Table 3–8. Datapath Interface for DDR2 and DDR SDRAM—nonAFI (Part 3 of 3)

(Note 1)

Signal Name

Type

Width

Description

Table 3–9. Calibration Status Interface for DDR2 and DDR SDRAM—nonAFI

Signal Name

Type

Width

Description

resynchronisation_

successful

output

1

Active-high signal that is set to indicate that

calibration of the read data resynchronization clock

phase was completed and successful.

postamble_successful

output

1

Active-high signal that is set to indicate that read

postamble calibration was completed.

tracking_successful

output

1

Active-high signal that is set to indicate the

completion of mimic path VT variation tracking

operation.

tracking_adjustment_

up

output

1

Active-high signal that is pulsed to indicate that the

mimic path tracking has adjusted the

resynchronization clock phasing upwards.

tracking_adjustment_

down

output

1

Active-high signal that is pulsed to indicate that the

mimic path tracking has adjusted the

resynchronization clock phasing downwards.