Altera External Memory PHY Interface User Manual

Page 40

3–24

Chapter 3: Functional Description—ALTMEMPHY (nonAFI)

ALTMEMPHY Signals

External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide

© January 2010

Altera Corporation

shows the parameters that

through

refer to.

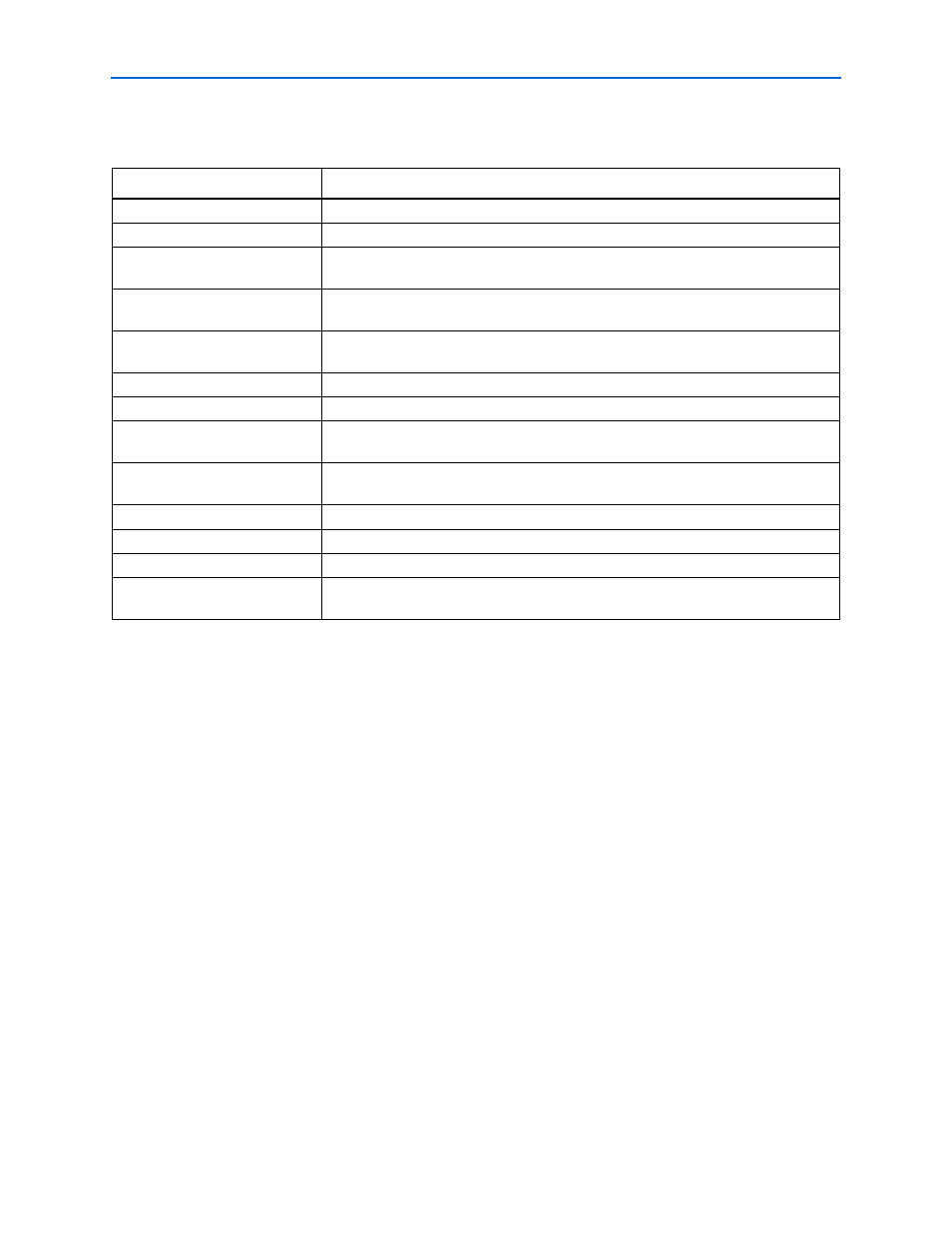

Table 3–16. Parameters

Parameter Name

Description

DBG_A_WIDTH

—

DQS_DELAY_CTL_WIDTH

—

DWIDTH_RATIO

The data width ratio from the local interface to the memory interface.

DWIDTH_RATIO

of 2 means full rate, while DWIDTH_RATIO of 4 means half rate.

LOCAL_IF_DWIDTH

The width of the local data bus must be quadrupled for half-rate and doubled for

full-rate.

MEM_IF_DWIDTH

The data width at the memory interface. MEM_IF_DWIDTH can have values that are

multiples of MEM_IF_DQ_PER_DQS.

MEM_IF_DQS_WIDTH

The number of DQS pins in the interface.

MEM_IF_ROWADDR_WIDTH

The row address width of the memory device.

MEM_IF_BANKADDR_WIDTH

The bank address with the memory device (not used in QDR II+/QDR II SRAM

variations).

MEM_IF_CS_WIDTH

The number of chip select pins in the interface. The sequencer only calibrates one chip

select pin.

MEM_IF_DM_WIDTH

The number of mem_dm pins on the memory interface.

MEM_IF_DQ_PER_DQS

The number of mem_dq[] pins per mem_dqs pin.

MEM_IF_CLK_PAIR_COUNT

The number of mem_clk/mem_clk_n pairs in the interface.

READ_LAT_WIDTH

The bus width for the ctl_rlat signal, used in QDR II+/QDR II SRAM PHY, that

determines the read latency of your system.