Altera External Memory PHY Interface User Manual

Page 30

3–14

Chapter 3: Functional Description—ALTMEMPHY (nonAFI)

ALTMEMPHY Signals

External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide

© January 2010

Altera Corporation

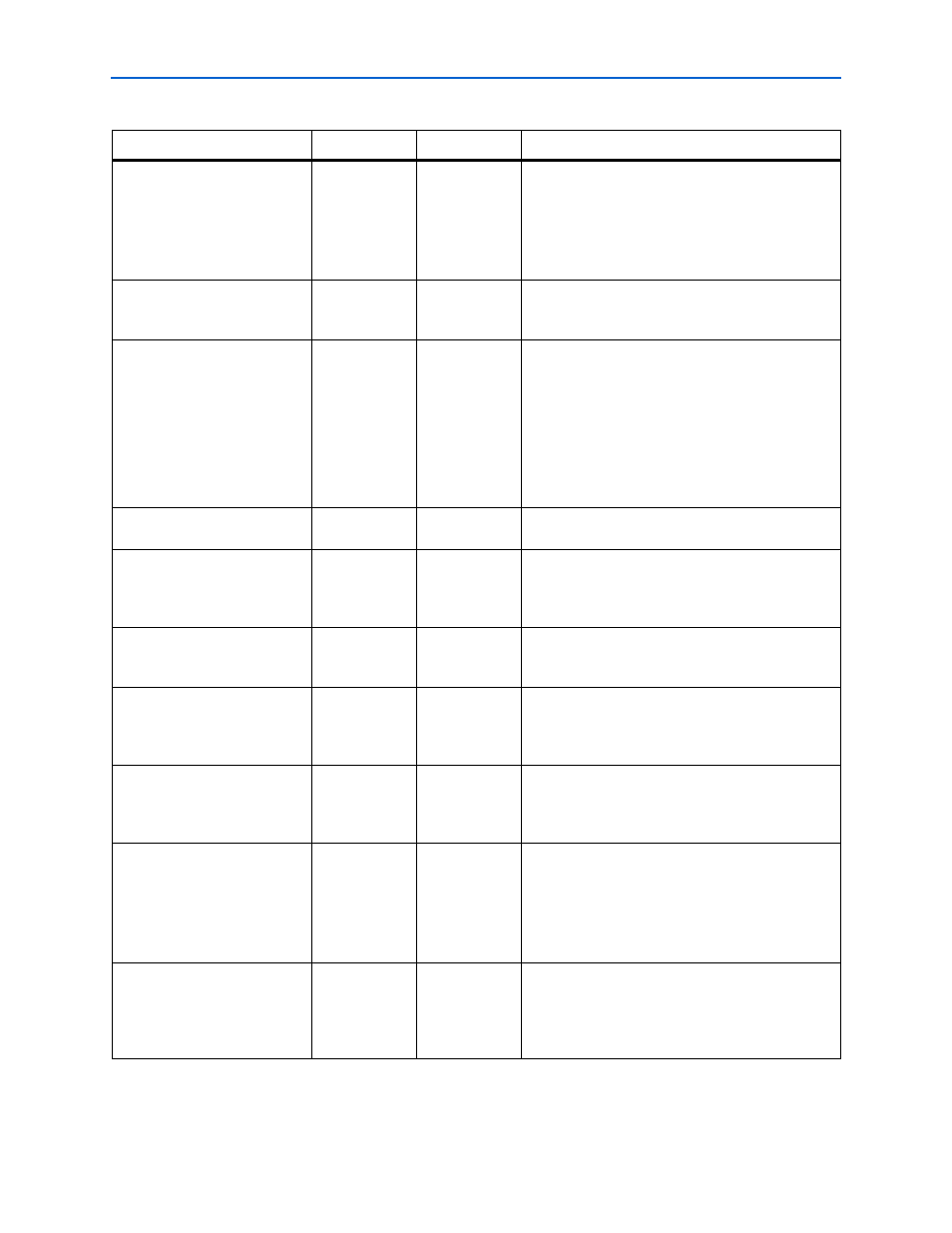

ctl_doing_rd

input

1

The active-high signal from the controller specifying

that a read command has been issued to the external

RAM.

For more information, see

Between Read Commands and Read Data” on

page 3–47

ctl_init_done

input

1

The memory controller drives this active-high signal

to specify that the controller has initialized the

memory and the calibration process should begin.

ctl_negedge_en

input

1

This signal is used if ADDR_CMD_NEGEDGE_EN is

set to EXT_SELECT. If true, the address and

command signals are output on the falling edge of

the address and command clock, ac_clk_2x. If

false, the address and command signals are output

on the rising edge of the address and command

clock. When set to EXT_SELECT, the

ctl_negedge_en

top level input determines

whether the edge is used.

ctl_read_req

output

1

The active-high signal requesting a read command to

the address on the ctl_address bus.

ctl_ready

input

1

The controller-ready signal which indicates that the

currently asserted read or write request has been

accepted. The address of the request is sampled

when both the ready and request signals are high.

ctl_size

output

LOCAL_

BURST_LEN_

BITS

The output to the controller indicating the size

(length) of the burst transfer, fixed at 1 for this

version.

ctl_usr_mode_rdy

output

1

The ALTMEMPHY sequencer logic drives this

active-high signal to specify the ALTMEMPHY has

finished its calibration and is ready to accept user

read or write requests.

ctl_wdata

output

LOCAL_IF_

DWIDTH

The write data from the ALTMEMPHY to the

controller. The ALTMEMPHY sequencer logic drives

ctl_wdata

during calibration. ctl_wdata has

the same timing as local_wdata.

ctl_wdata_req

input

1

The controller-request for write data; not required

when the controller has an Avalon-MM interface.

The memory controller that the ALTMEMPHY

sequencer uses during calibration drives

ctl_wdata_req

. Same timing as

local_wdata_req

.

ctl_write_req

output

1

The active-high signal specifying that a write

command should be issued to the address on the

ctl_address

signal. The ALTMEMPHY

sequencer logic drives ctl_write_req during

calibration. Same timing as local_write_req.

Table 3–6. Interface to the Memory Controller for DDR2 and DDR SDRAM—nonAFI

(Note 1)

(Part 2 of 3)

Signal Name

Type

Width

Description