Altera External Memory PHY Interface User Manual

Page 28

3–12

Chapter 3: Functional Description—ALTMEMPHY (nonAFI)

ALTMEMPHY Signals

External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide

© January 2010

Altera Corporation

The ports listed in

only exist when you target Stratix III and Stratix IV

devices. You can leave them unconnected if you are not using user-mode calibrated

OCT. For more information about Stratix III and Stratix IV ports, refer to

ALTMEMPHY Signals sect

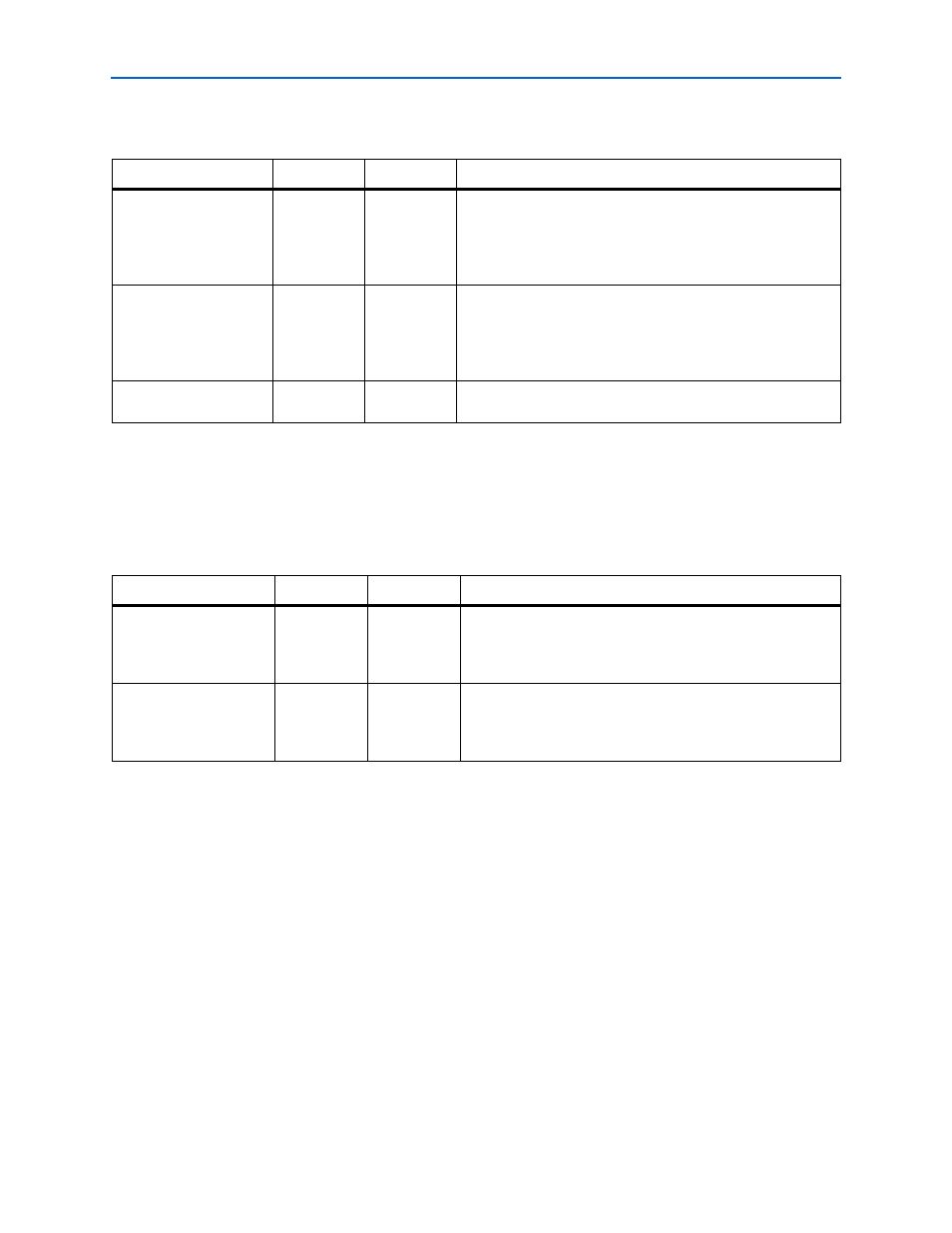

Table 3–4. External DLL Signals for DDR2 and DDR SDRAM—nonAFI

Signal Name

Type

Width

Description

dqs_delay_ctrl_

export

output

6

Allows sharing DLL in this ALTMEMPHY instance with another

ALTMEMPHY instance. Connect the

dqs_delay_ctrl_export

port on the ALTMEMPHY

instance with a DLL to the dqs_delay_ctrl_import port

on the other ALTMEMPHY instance.

dqs_delay_ctrl_

import

input

6

Allows the use of DLL in another ALTMEMPHY instance in this

ALTMEMPHY instance. Connect the

dqs_delay_ctrl_export

port on the ALTMEMPHY

instance with a DLL to the dqs_delay_ctrl_import port

on the other ALTMEMPHY instance.

dll_reference_

clk

output

1

Reference clock to feed to an externally instantiated DLL. This

clock is typically from one of the PHY PLL outputs.

Table 3–5. User-Mode Calibrated OCT Control Signals for DDR2/DDR SDRAM—nonAFI

Signal Name

Type

Width

Description

oct_ctl_rs_value

input

14

Specifies serial termination value. Connects to the

seriesterminationcontrol

bus of the ALT_OCT

megafunction. This port exists when you target Stratix IV and

Stratix III devices only.

oct_ctl_rt_value

input

14

Specifies parallel termination value. Connects to the

parallelterminationcontrol

bus of the ALT_OCT

megafunction. This port exists when you target Stratix IV and

Stratix III devices only.

Notes to

(1) These ports are available if you want to use user-mode OCT calibration. Otherwise, they can be left unconnected.

(2) For more information on OCT, see