Note 1) – Altera External Memory PHY Interface User Manual

Page 31

Chapter 3: Functional Description—ALTMEMPHY (nonAFI)

3–15

ALTMEMPHY Signals

© January 2010

Altera Corporation

External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide

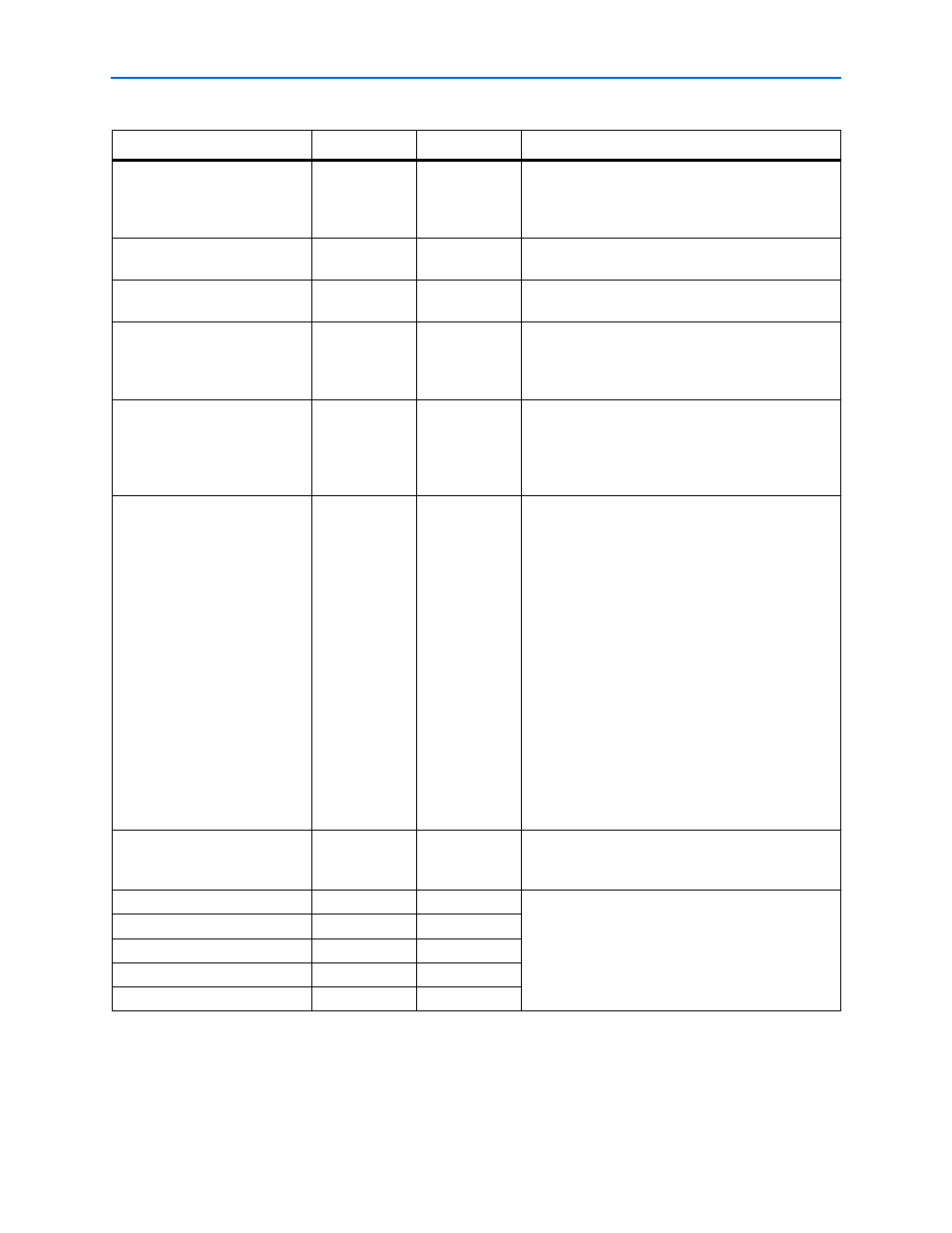

ctl_refresh_ack

input

1

The active-high valid signal from the controller

acknowledging the refresh request. The

ALTMEMPHY sequencer logic uses

ctl_refresh_ack

during calibration.

ctl_refresh_req

output

1

The output to the controller requesting a refresh.

Same timing as local_refresh_req.

ctl_burstbegin

output

1

The output to the controller indicating the start of a

burst. Only available for the Avalon-MM interface.

ctl_rdata

input

LOCAL_IF_

DWIDTH

The read data from the controller. The ALTMEMPHY

sequencer logic uses ctl_rdata during

calibration. ctl_rdata has the same timing as

local_rdata

.

ctl_rdata_valid

input

1

The active-high valid signal for the controller read

data. Asserted coincident with the read data on

ctl_rdata

. The controller drives

ctl_rdata_valid

and has the same timing as

local_rdata_valid

.

ctl_add_1t_odt_lat

input

1

When asserted, one extra address and command

clock cycle (1T) of latency is inserted in the address

and command ODT path if ODT_ADD_1T is set to

EXT_SELECT

, see

Between Write Commands and Write Data” on

page 3–49

The timing of the mem_odt signal can be controlled

in the same way as mem_addr, but is independent

of the address and command latency. If the

ODT_ADD_1T

parameter is set to EXT_SELECT,

an extra cycle of latency can be dynamically inserted

on the ODT command outputs by asserting the

ctl_add_1t_odt_lat

input, which allows

separate run-time control of the latency of the ODT

signal. If ODT_ADD_1T is set to TRUE, the extra

clock cycle of latency is always present. If

ODT_ADD_1T

is set to FALSE, the extra latency is

never added.

ctl_rlat

output

READ_LAT_

WIDTH

Unused port that exists when you target Stratix IV

and Stratix III devices. The default

READ_LAT_WIDTH

is set to 4.

ctl_self_rfsh_ack

input

1

Signal from the Altera high-performance controller

that is passed through the PHY.

ctl_powerdn_ack

input

1

ctl_autopch_req

output

1

ctl_powerdn_req

output

1

ctl_self_rfsh_req

output

1

Note to

(1) Interface signals to the controller either through the sequencer or user interface.

Table 3–6. Interface to the Memory Controller for DDR2 and DDR SDRAM—nonAFI

(Note 1)

(Part 3 of 3)

Signal Name

Type

Width

Description