Document revision history – Altera Phase-Locked Loop Reconfiguration IP Core User Manual

Page 50

Page 50

Document Revision History

Phase-Locked Loop Reconfiguration (ALTPLL_RECONFIG) Megafunction

February 2012

Altera Corporation

Document Revision History

lists the revision history for this document.

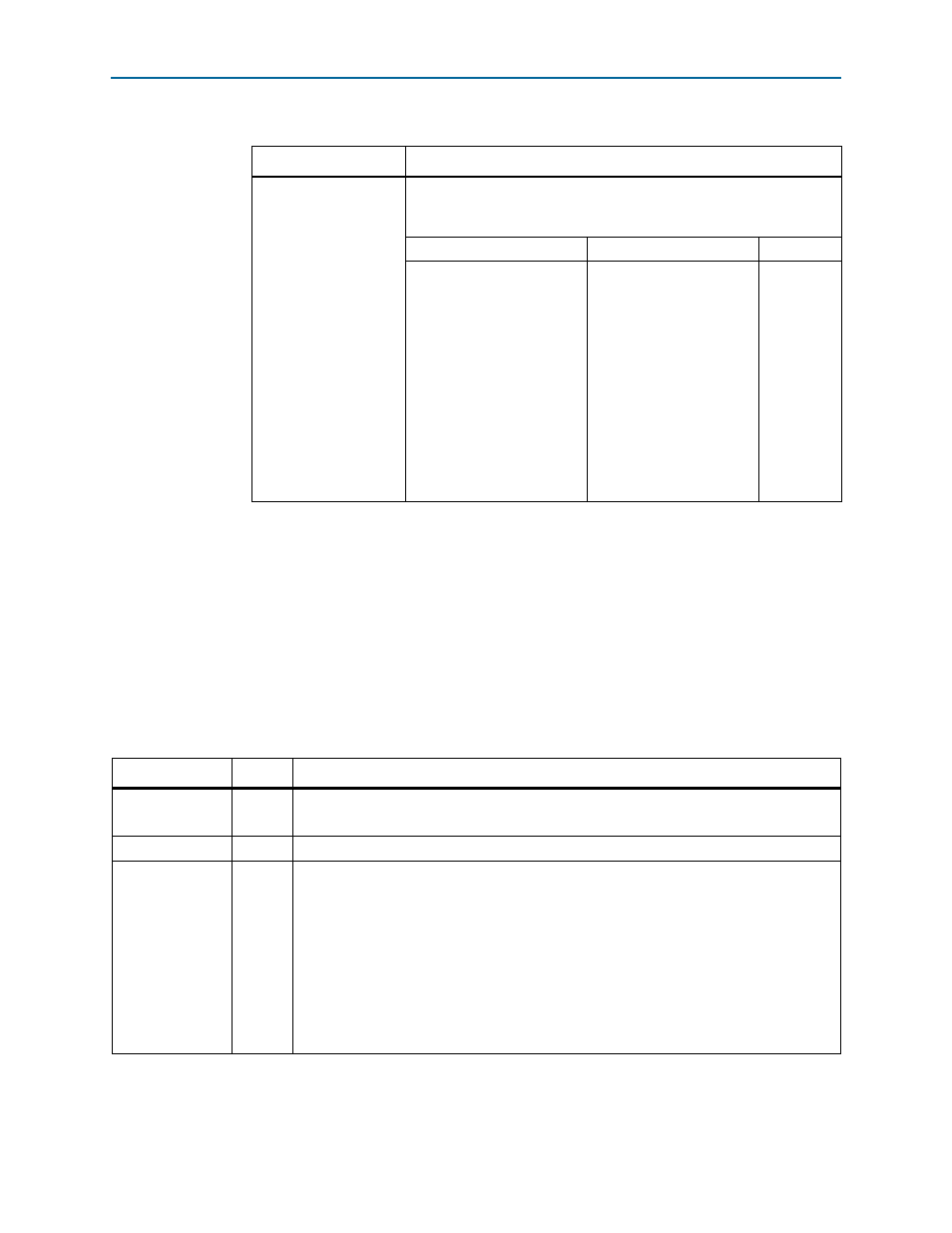

counter_param[]

3-bit bus that selects which parameter for the given counter type should

be updated. The mapping to each parameter type and the corresponding

parameter bit-width is defined as follows:

counter_param[2..0]

Selected Parameter

Width

000 (0x0)

001 (0x1)

000 (0x0)

001 (0x1)

010 (0x2)

011 (0x3)

100 (0x4)

101 (0x5)

110 (0x6)

111 (0x7)

spread count

high cycles count

low cycles count

delay element setting

(illegal value)

counter bypass bit

counter odd division bit

(illegal value)

(illegal value)

9

9

9

9

4

—

1

1

—

—

Notes to

:

(1) The lower 2 bits indicate the counter number for the

G

,

L

, and

E

counters. Additionally, the

Ex

counters are only

valid for the

LONG

scan chain PLLs.

(2) For

M

and

N

.

(3) For

G

,

L

, and

E

.

(4) Must be 0 for

M

or

N

.

(5) The upper 2 bits determine the width (for example, 00× = 9, 01× = 4, 10× = 1)

Table 14. counter_type and counter_param Settings for Stratix and Stratix GX Devices (Part 2

of 2)

Counter

Settings

Table 15. Document Revision History (Part 1 of 2)

Date

Version

Changes

February 2012

6.0

■

Added information about nominal count usage in

■

Updated the decimal value in

August 2010

5.0

Updated for the Quartus II software version 10.0.

July 2008

4.0

■

Added support for Stratix IV devices.

■

Updated screenshots for “MegaWizard Plug-In Manager Page Descriptions” section.

■

Updated

section.

■

Updated “General Description” section.

■

Added

section.

■

Added

“Checking Design Violations With the Design Assistant”

section

■

Added comment for

pll_scanclk

port.

■

Added support for new port,

pllena

.