Simulating the design example – Altera Phase-Locked Loop Reconfiguration IP Core User Manual

Page 19

Design Example

Page 19

Phase-Locked Loop Reconfiguration (ALTPLL_RECONFIG) Megafunction

February 2012

Altera Corporation

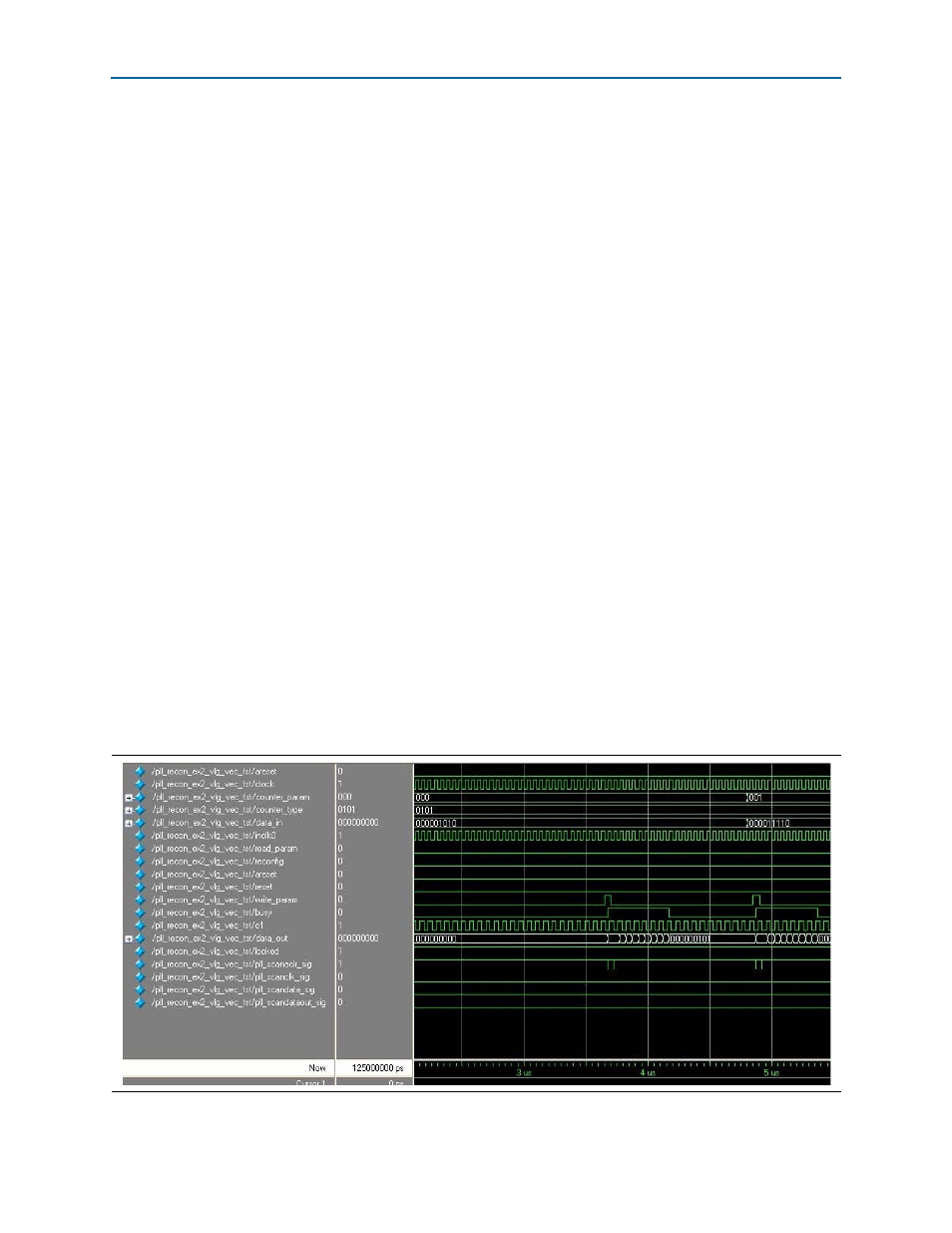

Simulating the Design Example

To simulate the design example using the ModelSim-Altera software, follow these

steps:

1. Unzip the altpll_reconfig_ex2_msim.zip

file to any working directory on your

PC.

2. Browse to the folder in which you unzipped the files.

3. Open the remote_update_ex2.do file in a text editor.

4. In line 1 of the altpll_reconfig_ex2_msim.do file, make sure the directory path of

the library files is correct. For example, C:/Modeltech_ae/altera/verilog/stratix.

5. On the File menu, click Save.

6. Launch the ModelSim-Altera software.

7. On the File menu, click Change Directory.

8. Select the folder in which you unzipped the files.

9. Click OK.

10. On the Tools menu, click Execute Macro.

11. Select the altpll_reconfig_ex2_msim.do file and click Open. This is a script file for

ModelSim-Altera software to automate all of the necessary settings for the

simulation.

12. Verify the results shown in the Wave window.

You can rearrange, remove, and add signals. and change the radix by modifying the

script altpll_reconfig_ex2_msim.do.

through

show the expected simulation results in the

ModelSim-Altera software. The duty cycle changes from a ratio of 50:50 to 25:75 and

finally to 75:25.

Figure 14. Changing Parameters (2.11 to 7.23 ms)