Altera Phase-Locked Loop Reconfiguration IP Core User Manual

Page 5

Checking Design Violations With the Design Assistant

Page 5

Phase-Locked Loop Reconfiguration (ALTPLL_RECONFIG) Megafunction

February 2012

Altera Corporation

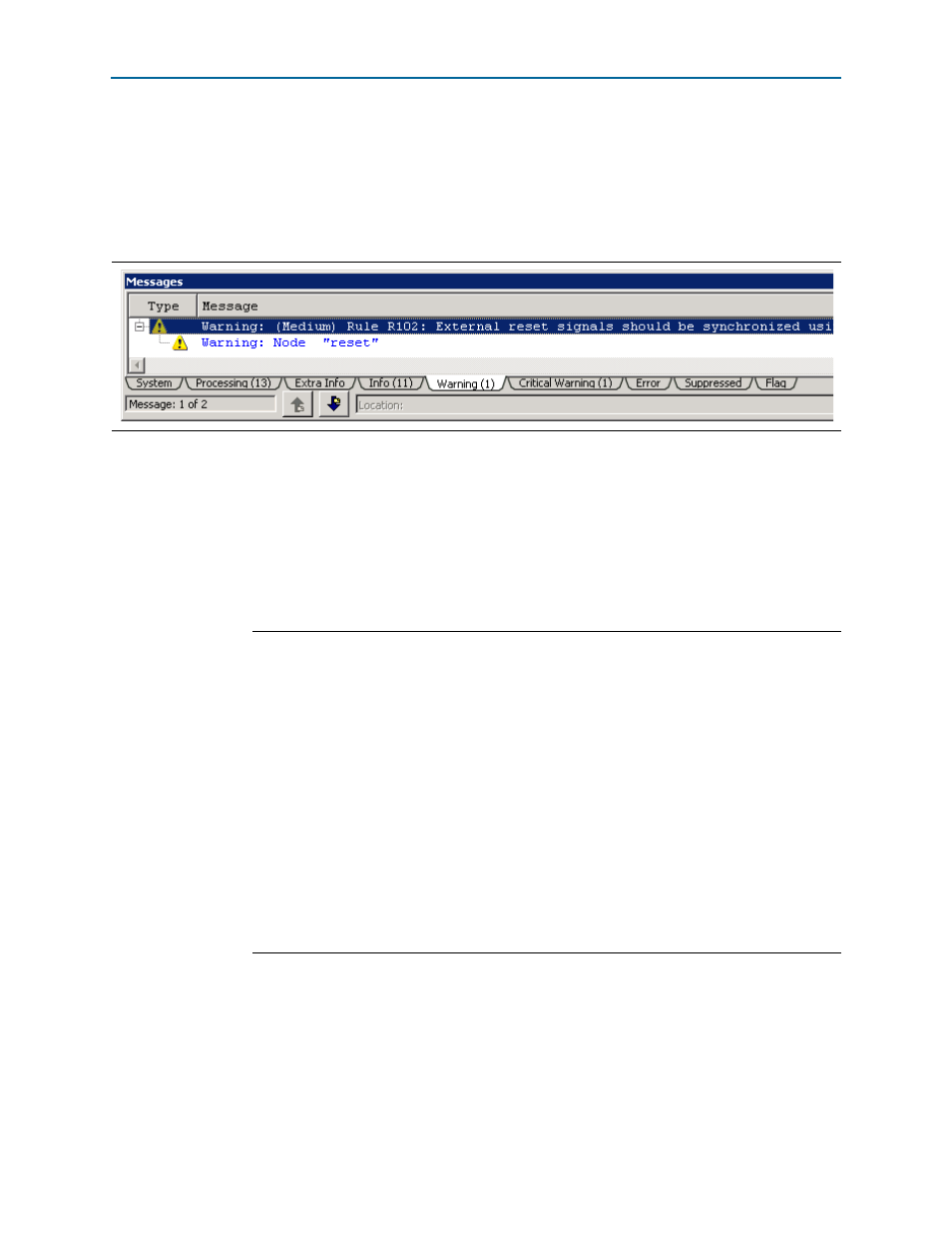

Checking Design Violations With the Design Assistant

The Design Assistant is a design rule checking tool that allows you to check for design

issues early in the design flow. When you run the Design Assistant in the Quartus II

software for the ALTPLL_RECONFIG megafunction, you might receive the warning

message shown in

This message appears because there is a combinational logic in the megafunction that

connects the synchronous signal to the asynchronous external reset signal. To fix the

issue, you must synchronize the external reset signal outside the megafunction.

To synchronize the external reset signal, use the sample Verilog HDL code shown in

. In the example, the input of

sync_reset_dffe1

is connected to the external

reset pin, and the output of

sync_reset_dffe2

is connected to the

reset

input port of

the ALTPLL_RECONFIG megafunction.

Figure 2. Warning Message in Design Assistant

Example 1. Code to Synchronize External Reset Signal

module synch_reg (reset, reconfig_clk, sync_reset_dffe2);

input reset, reconfig_clk;

output sync_reset_dffe2;

reg sync_reset_dffe1, sync_reset_dffe2;

always @(posedge reconfig_clk)

begin

sync_reset_dffe1 = reset;

end

always @(posedge reconfig_clk)

begin

sync_reset_dffe2 = sync_reset_dffe1;

end

endmodule