Altera Phase-Locked Loop Reconfiguration IP Core User Manual

Page 45

Specifications

Page 45

Phase-Locked Loop Reconfiguration (ALTPLL_RECONFIG) Megafunction

February 2012

Altera Corporation

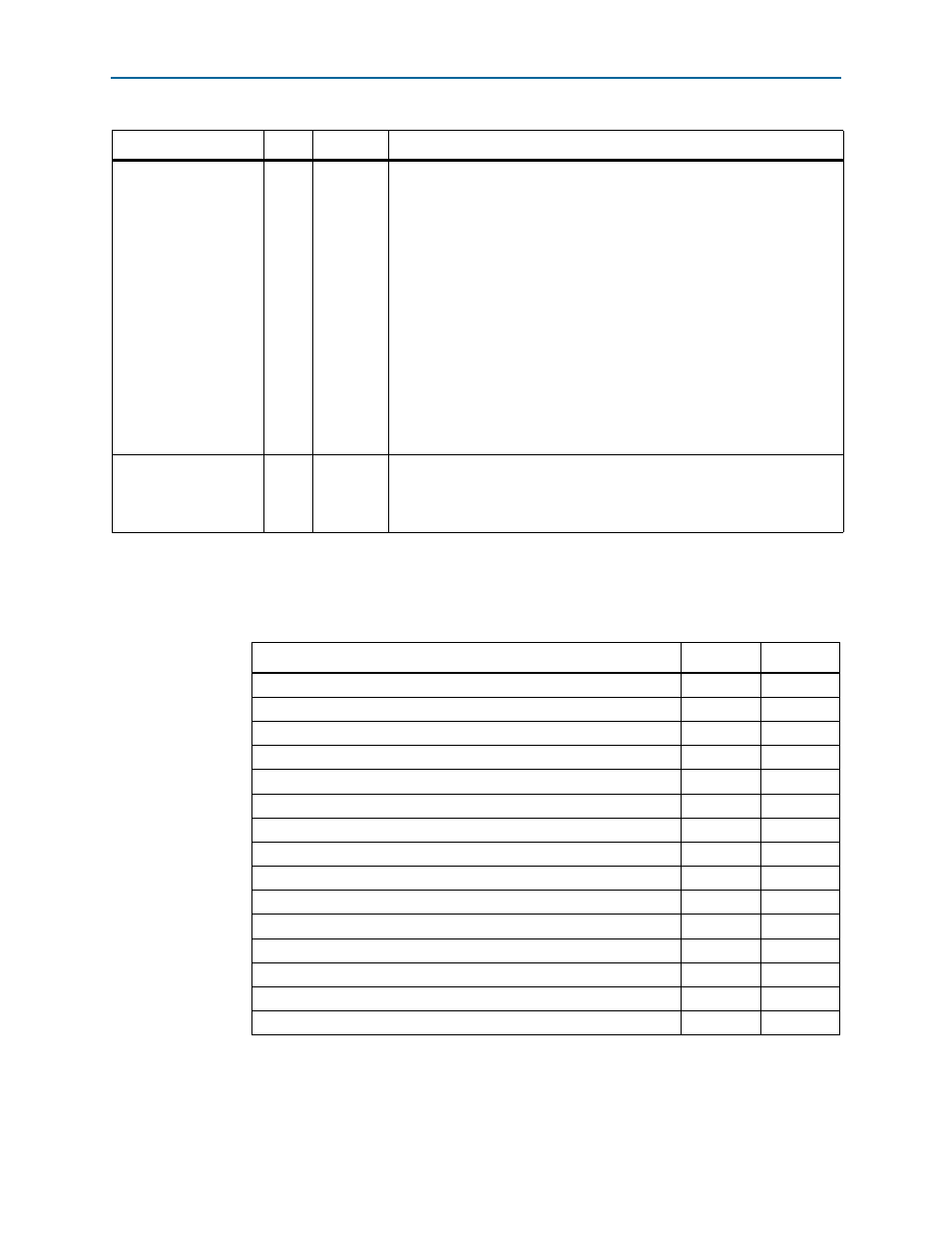

lists the

counter_type

settings for Stratix III, Stratix IV, Cyclone III,

Cyclone IV, and Arria II GX devices.

scan_init_file

String No

Specifies the name of the .mif or .hex used as the initial value of the scan

chain cache. Values are

UNUSED

. If omitted, the value for

every entry in the cache is

0

. You must set the input file as shown in the

following table:

Device

Input File Size

Stratix series devices

(except Stratix III and Stratix IV

devices)

192 bits or 288 bits depending on

the

scan_chain

length

Stratix III and Stratix IV Top/Bottom

PLL devices

234 bits

Stratix III and Stratix IV Right/Left

PLL devices

180 bits

Cyclone III and Cyclone IV devices

144 bits

Arria II GX devices

180 bits

use_scanclk_sync_

register

String No

Specifies whether to use the

scanclk

port for the synchronization mode for

the register. Available for all supported devices except Stratix III, Stratix IV,

Cyclone III, Cyclone IV, HardCopy III, HardCopy IV, and Arria II GX devices.

Values are

YES

and

NO

. If omitted, the default value is

NO

.

Table 10. ALTPLL_RECONFIG Megafunction Parameters (Part 2 of 2)

Parameter

Type

Required?

Description

Table 11. counter_type[3..0] Settings for Stratix III, Stratix IV, Cyclone III, Cyclone IV, and

Arria II GX Devices (Part 1 of 2)

Counter Selection

Binary

Decimal

N

0000

0

M

0001

1

CP/LF

0010

2

VCO

0011

3

C0

0100

4

C1

0101

5

C2

0110

6

C3

0111

7

C4

1000

8

C5

1001

9

C6

1010

10

C7

1011

11

C8

1100

12

C9

1101

13

Illegal value

1110

14