Altera Phase-Locked Loop Reconfiguration IP Core User Manual

Page 48

Page 48

Specifications

Phase-Locked Loop Reconfiguration (ALTPLL_RECONFIG) Megafunction

February 2012

Altera Corporation

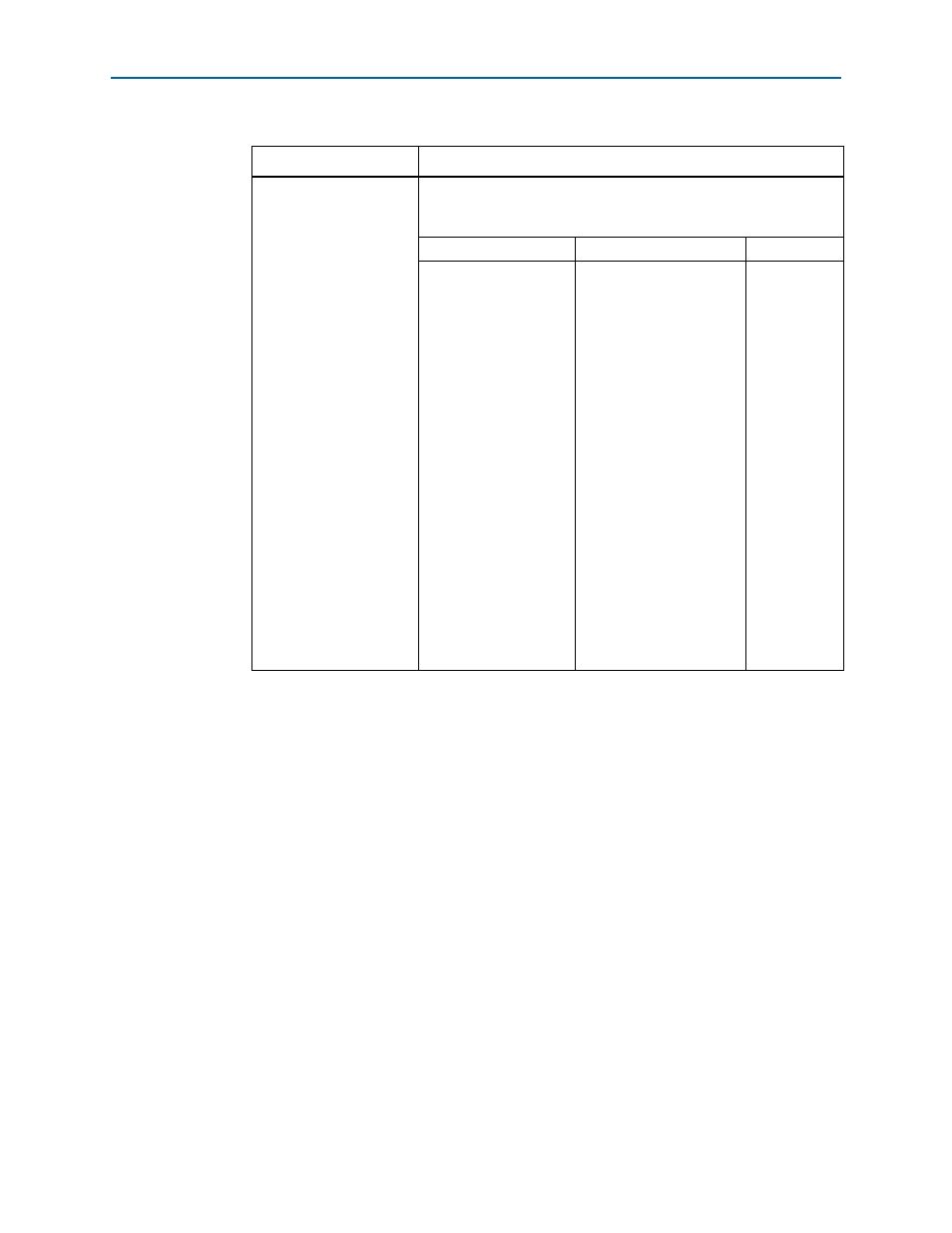

counter_param[]

3-bit bus that selects which parameter for the given counter type

should be updated. The mapping to each parameter type and the

corresponding parameter bit-width is defined as follows:

counter_param[2..0]

Selected Parameter

Width

000 (0x0)

001 (0x1)

000 (0x0)

001 (0x1)

000 (0x0)

001 (0x1)

000 (0x0)

010 (0x2)

100 (0x4)

101 (0x5)

101 (0x5)

000 (0x0)

001 (0x1)

010 (0x2)

011 (0x3)

110 (0x6)

111 (0x7)

nominal count

high cycles count

low cycles count

high cycles count

low cycles count

nominal count

phase step setting

counter bypass bit

counter odd division bit

spread counter bypass

charge pump current

loop filter resistor

loop filter capacitor

(illegal value)

(illegal value)

(illegal value)

9

9

8

8

4

4

2

2

1

1

1

4

6

2

—

—

—

Notes to

:

(1) For Enhanced PLL

M

and

N

.

(2) For Enhanced PLL

C0

-

C5

.

(3) For Fast PLL

C0

-

C3

and

M

.

(4) For Fast PLL

N

.

(5) For

C0

-

C5

, Fast PLL

M

.

(6) For CP/LF.

Table 13. counter_type and counter_param Settings for Stratix II, Stratix II GX, Arria GX, and

HardCopy II Devices (Part 2 of 2)

Counter

Settings