Altera Phase-Locked Loop Reconfiguration IP Core User Manual

Page 43

Specifications

Page 43

Phase-Locked Loop Reconfiguration (ALTPLL_RECONFIG) Megafunction

February 2012

Altera Corporation

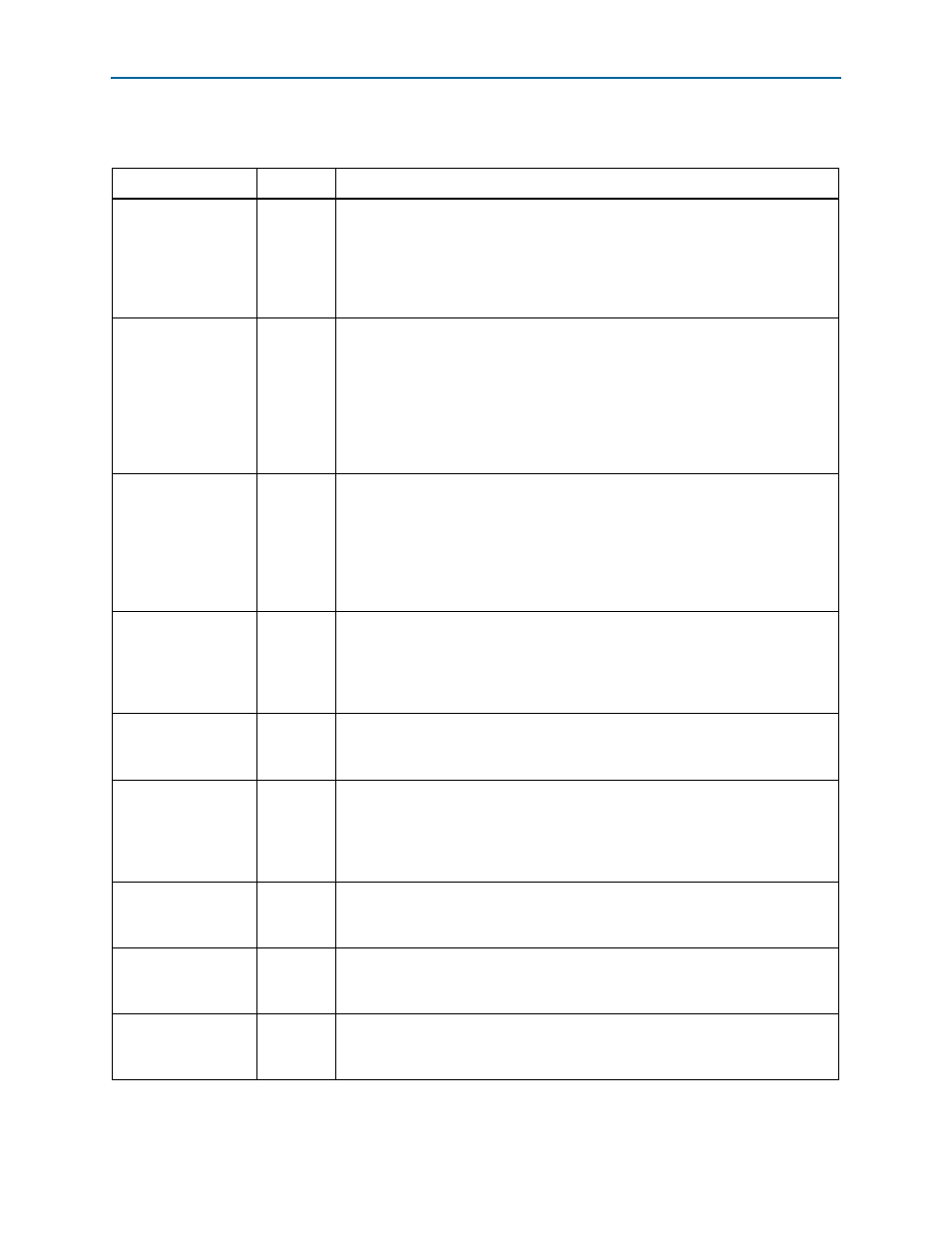

lists the ALTPLL_RECONFIG megafunction output ports.

Table 9. ALTPLL_RECONFIG Megafunction Output Ports (Part 1 of 2)

Port Name

Required?

Description

data_out[]

No

Data read from the cache when

read_param

is asserted.

9-bit output bus that provides the parameter data to the user. When the

read_param

signal is asserted, the values on

counter_type[]

and

counter_param[]

determine

the parameter value that is loaded from cache and driven on the

data_out[]

bus.

When the megafunction deasserts the

busy

signal, the appropriate bits of the bus

(for example,

[0]

or

[3..0]

) hold a valid value.

busy

No

Indicates when the PLL is reading or writing a parameter to the cache, or is

configuring the PLL.

While the

busy

signal is asserted, no parameters can be read or written, and no

reconfiguration can be initiated. Changes to the megafunction can be made only

when the

busy

signal is not asserted. The signal goes high when the

read_param

,

write_param

, or

reconfig

input port is asserted, and remains high until the

specified operation is complete. In the case of a reconfiguration operation, the

busy

signal remains high until the

pll_areset

signal is asserted and then deasserted.

pll_areset

Yes

Drives the

areset

port on the PLL to be reconfigured.

The

pll_areset

port must be connected to the

areset

port of the ALTPLL

megafunction for the reconfiguration to function correctly. This signal is active high.

pll_areset

is asserted when

pll_areset_in

is asserted, or, after reconfiguration,

at the next rising clock edge after the

scandone

signal goes high. If you use the

ALTPLL_RECONFIG megafunction, drive the PLL areset port using the

pll_areset

output port.

pll_configupdate

No

Drives the

configupdate

port on the PLL to be reconfigured.

When asserted, the

pll_configupdate

port loads selected data to PLL

configuration latches. The signal is asserted after the final data bit is sent out. This

port is available for Stratix III, Stratix IV, Cyclone III, Cyclone IV, HardCopy III,

HardCopy IV, and Arria II GX devices only.

pll_scanclk

Yes

Drives the

scanclk

port on the PLL to be reconfigured.

For information about the maximum

scanclk

frequency for the various devices,

refer to the respective device handbook.

pll_scanclkena

No

This acts as a clock enable for the

scanclk

port on the PLL to be reconfigured.

Reconfiguration begins on the first rising edge of

pll_scanclk

after

pll_scanclkena

is asserted. On the first falling edge of

pll_scanclk

, after the

pll_scanclkena

signal is deasserted, the megafunction stops scanning data to the

PLL.

pll_scanaclr

Yes

Drives the

scanaclr

port on the PLL to be reconfigured.

Not available for Stratix II, Stratix III, Stratix IV, Cyclone III, Cyclone IV, HardCopy II,

HardCopy III, HardCopy IV, Arria GX, and Arria II GX devices.

pll_scanread

No

Drives the

scanread

port on the PLL to be reconfigured.

Not available for Stratix III, Stratix IV, Cyclone III, Cyclone IV, HardCopy III,

HardCopy IV, and Arria II GX devices.

pll_scanwrite

No

Drives the

scanwrite

port on the PLL to be reconfigured.

Not available for Stratix III, Stratix IV, Cyclone III, Cyclone IV, HardCopy III,

HardCopy IV, and Arria II GX devices.