Altera Phase-Locked Loop Reconfiguration IP Core User Manual

Page 12

Page 12

Design Example

Phase-Locked Loop Reconfiguration (ALTPLL_RECONFIG) Megafunction

February 2012

Altera Corporation

7. Click Finish. The

reconfig_pll

module is built.

8. Click OK. The MegaWizard Plug-In Manager resets to page 2a to allow you to

create a new custom megafunction variation.

9. In the MegaWizard Plug-In Manager pages, select or verify the configuration

settings listed in

. Click Next to advance from one page to the next.

10. Click Finish. The

pll_reconfig

module is built.

Summary

Variation file

Turned on

PinPlanner ports PPF file

Turned on

AHDL Include file

Turned on

VHDL component declaration file

Turned on

Quartus II symbol file

Turned on

Instantiation template file

Turned on

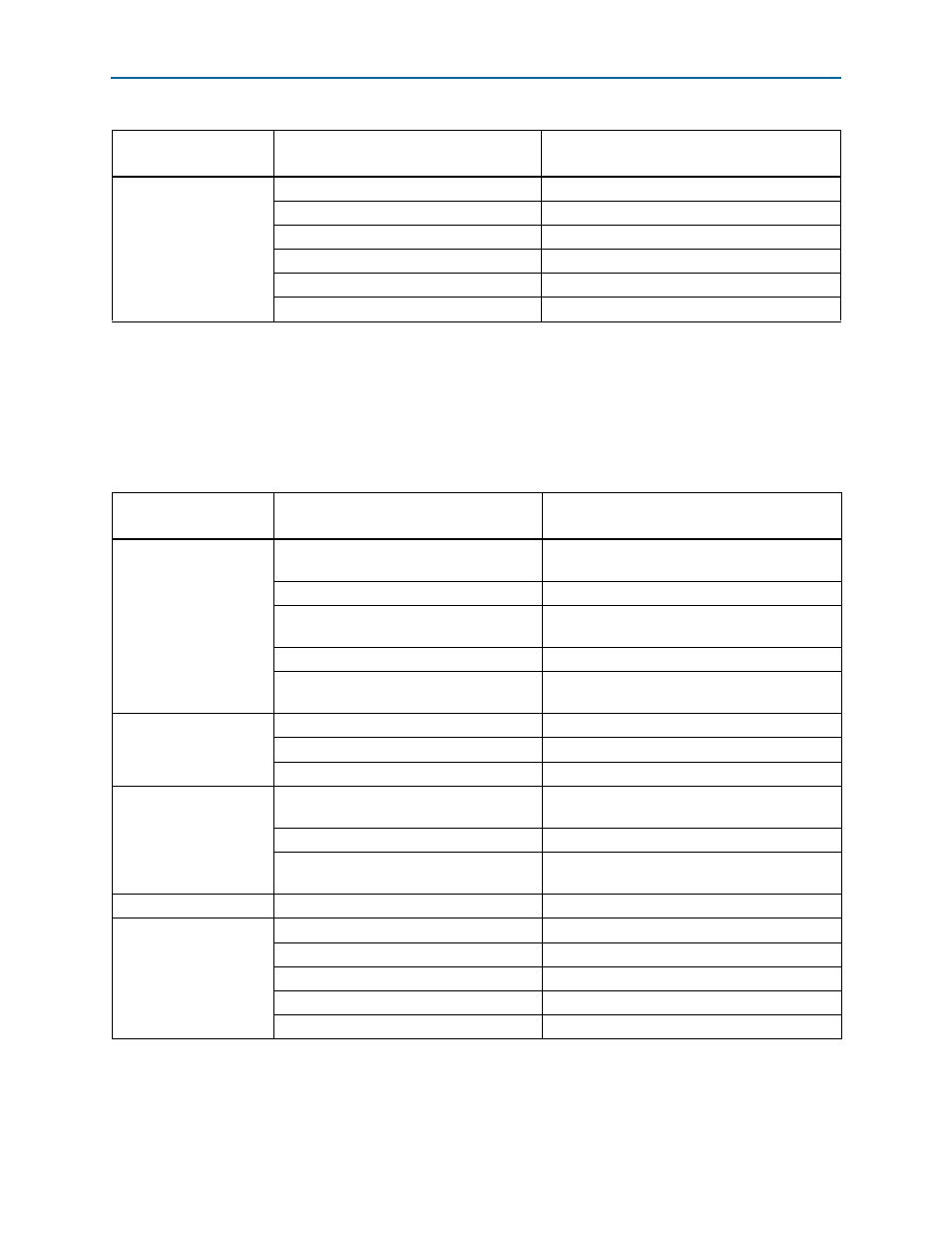

Table 2. Configuration Settings for the ALTPLL Megafunction (Part 2 of 2)

MegaWizard Plug-In

Manager Page

Settings

Value

Table 3. Configuration Settings for the ALTPLL_RECONFIG Megafunction

MegaWizard Plug-In

Manager Page

Settings

Value

2a

Megafunction

Under the I/O category, select

ALTPLL_RECONFIG

Which device family will you be using?

Stratix

Which type of output file do you want to

create?

VHDL

What name do you want for the output file?

pll_reconfig

Return to this page for another create

operation

Turned off

Parameter Settings

(General)

Currently selected device family

Stratix

Match project/default

Turned on

Which scan chain type will you be using

Long chain

Parameter Settings

(General 2)

Do you want to specify initial value of the

scan chain?

Select Yes, use this file for the content data

File name

pll_j1__clk0.mif

Do not use pre initialized RAM - initialize

from ROM instead

Turned off

EDA

Generate netlist

Turned off

Summary

Variation file

Turned on

AHDL Include file

Turned on

VHDL component declaration file

Turned on

Quartus II symbol file

Turned on

Instantiation template file

Turned on