Altera Phase-Locked Loop Reconfiguration IP Core User Manual

Page 44

Page 44

Specifications

Phase-Locked Loop Reconfiguration (ALTPLL_RECONFIG) Megafunction

February 2012

Altera Corporation

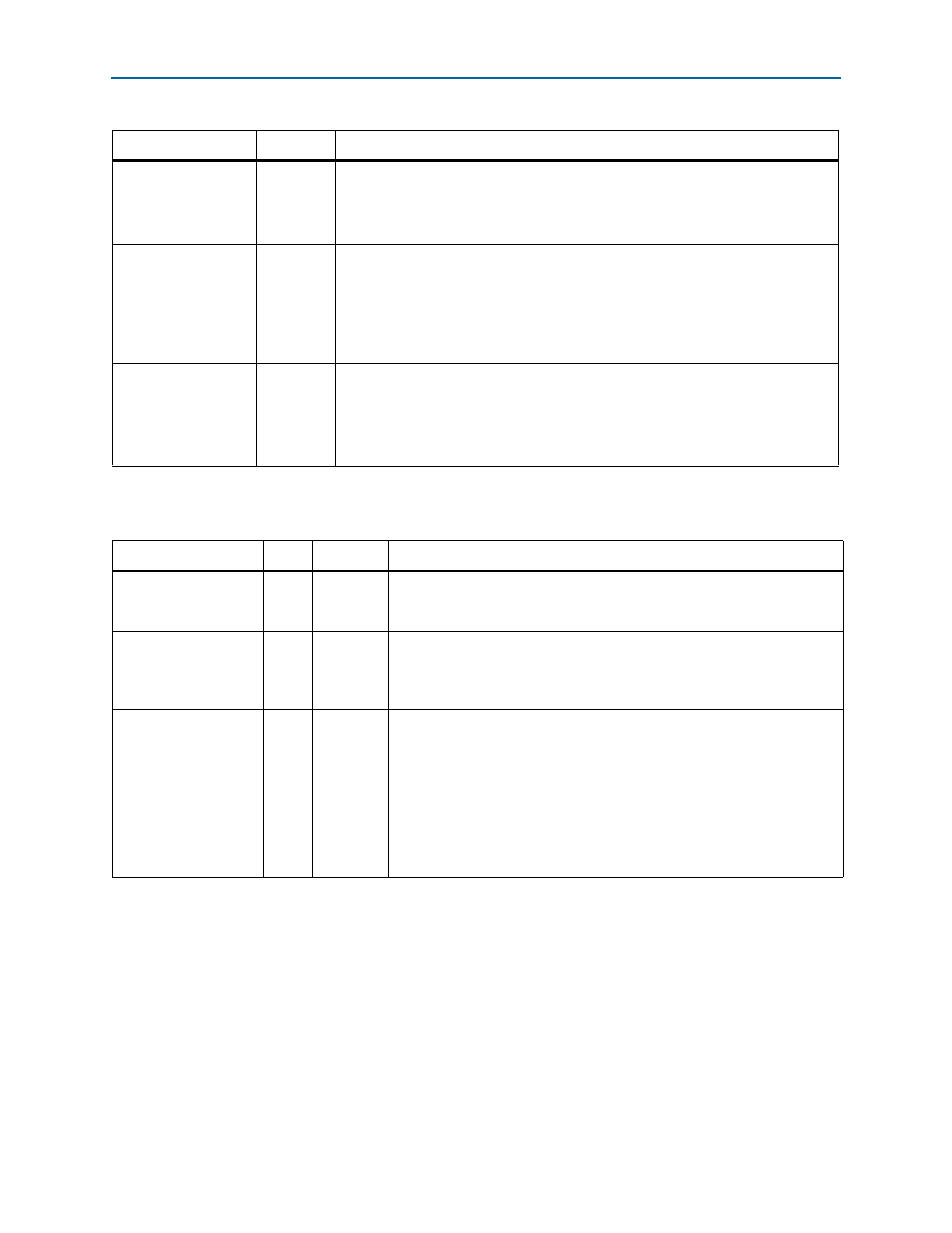

lists the ALTPLL_RECONFIG megafunction parameters.

pll_scandata

Yes

Drives the

scandata

port on the PLL to be reconfigured.

This output port from the megafunction holds the scan data input to the PLL for the

dynamically reconfigurable bits. The

pll_scandata

port sends scandata to the PLL.

Any activity on this port can only be observed when the

reconfig

signal is asserted.

rom_address_out

No

Specifies the address in ROM from which data is written to the scan chain.

During the write operation, the address increments from address 0 to the size of the

scan cache. The

rom_address_out

port is valid only while the

write_rom_ena

port

is asserted. Each address is asserted for 1 clock cycle. This port is available for

Stratix III, Stratix IV, Cyclone III, Cyclone IV, HardCopy III, HardCopy IV, and Arria II

GX devices only.

write_rom_ena

No

Enables the ROM.

When the

write_rom_ena

signal is asserted, the ALTPLL_RECONFIG

megafunctions generates valid addresses on the

rom_address_out

port. This port

is available for Stratix III, Stratix IV, Cyclone III, Cyclone IV, HardCopy III,

HardCopy IV, and Arria II GX devices only.

Table 9. ALTPLL_RECONFIG Megafunction Output Ports (Part 2 of 2)

Port Name

Required?

Description

Table 10. ALTPLL_RECONFIG Megafunction Parameters (Part 1 of 2)

Parameter

Type

Required?

Description

init_from_rom[]

String No

Specifies initialization from ROM. Initializes on power-up and not after every

reset (to match RAM .mif file behavior). The available values are

YES

and

NO

. If omitted, the default value is

NO

.

pll_type

String No

Specifies the type of PLL to instantiate. For Stratix III, Stratix IV, Cyclone III,

Cyclone IV, Arria II GX, HardCopy III, and HardCopy IV devices, values are

TOP_BOTTOM

and

LEFT_RIGHT

. For Stratix II, Stratix II GX, Arria GX, and

HardCopy II devices, values are

ENHANCED

and

FAST.

scan_chain

String No

Specifies the valid PLL types. Available for Stratix and Stratix GX devices

only. Values are

LONG

,

SHORT

, and

UNUSED

. If omitted, the default value is

UNUSED

.

Value

Configuration Setting

LONG

288-bit scan chain used to control

PLLs with 12 counters

SHORT

192-bit scan chain used to control

PLLs with 8 counters