Altera Phase-Locked Loop Reconfiguration IP Core User Manual

Page 42

Page 42

Specifications

Phase-Locked Loop Reconfiguration (ALTPLL_RECONFIG) Megafunction

February 2012

Altera Corporation

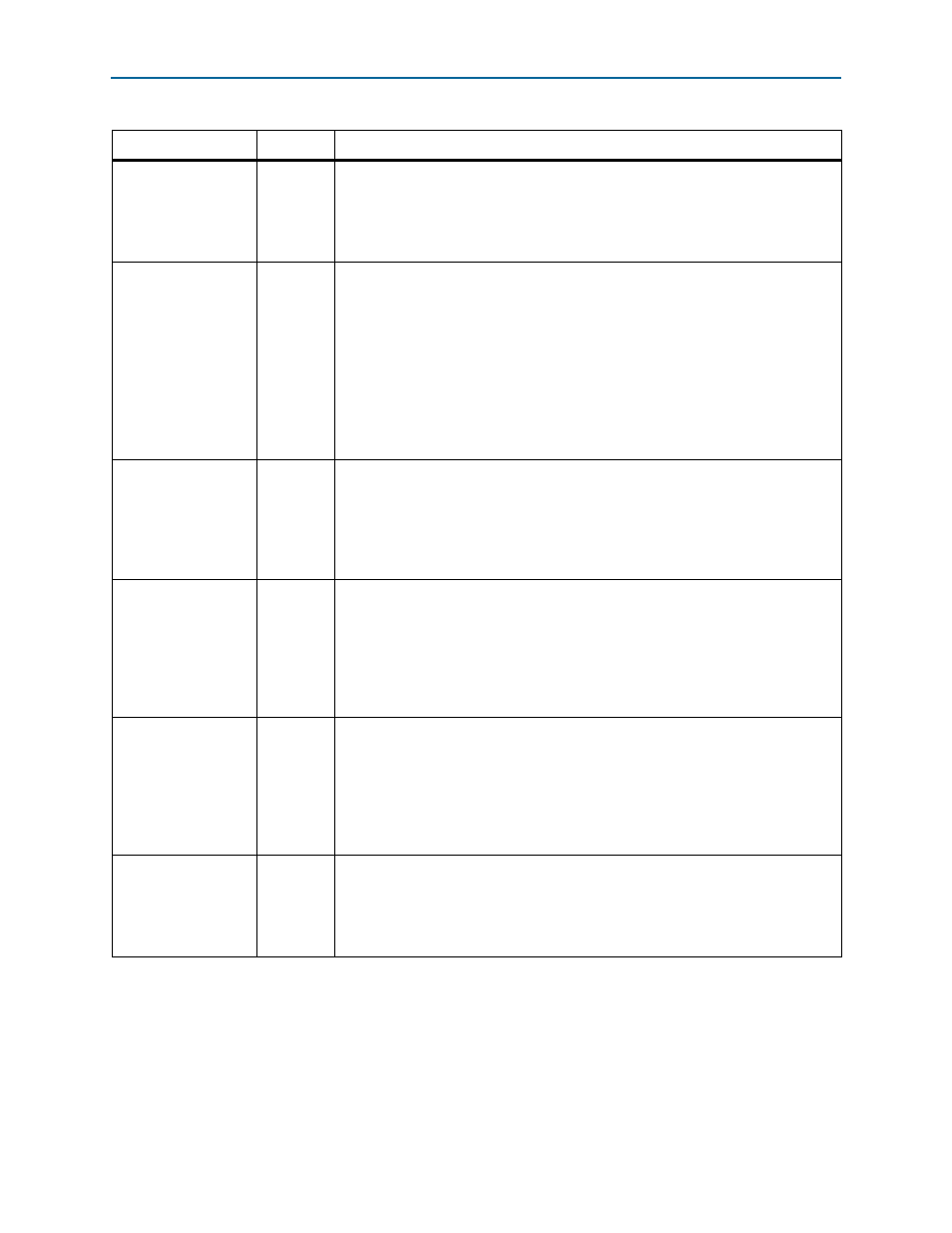

pll_areset_in

No

Input signal indicating that the PLL should be reset.

When asserted, the

pll_areset_in

signal indicates the PLL megafunction should

be reset. This port defaults to

0

if left unconnected. When the ALTPLL_RECONFIG

megafunction is used in a design, you cannot reset the PLL in any other way; you

must use this megafunction port to manually reset the PLL.

pll_scandone

No

Input port for the ALTPLL_RECONFIG megafunction that signals update done from

the PLL module. This port is driven by the PLL's

scandone

output signal and

determines when the PLL is reconfigured.

For Stratix III and Stratix IV devices,

pll_scandone

is asserted on most operations,

and deasserted as soon as it detects the assertion of

configupdate

. Upon the

completion of all PLL reconfiguration updates,

scandone

is reasserted.

This is different than the

scandone

signal in older device families, such as Stratix

devices. In Stratix devices, the

scandone

signal is deasserted most of the time. The

scandone

signal is asserted for 1 clock cycle to mark the completion of PLL

reconfiguration.

pll_scandataout

Yes

Input port driven by the

scandataout

signal from the ALTPLL megafunction. It can

be used to read the current configuration of the ALTPLL megafunction.

This input port holds the ALTPLL megafunction scan data output from the

dynamically reconfigurable bits. The

pll_scandataout

port must be connected to

the

scandataout

port of the PLL. The activity on this port can only be observed

when the

reconfig

signal is asserted.

rom_data_in

No

Serial data input to the PLL from the ROM.

This 1-bit port allows the external ROM to be serially written into the scan cache of

the ALTPLL_RECONFIG megafunction. The value on this port is valid 2 clock cycles

after the

write_rom_ena

signal is asserted and remains valid until 2 clock cycles

after the

write_rom_ena

signal is deasserted. This port is available for Stratix III,

Stratix IV, Cyclone III, Cyclone IV, HardCopy III, HardCopy IV, and Arria II GX devices

only.

write_from_rom

No

Specifies that the scan chain must be written from the external ROM.

When asserted, this signal tells the ALTPLL megafunction to write the scan cache

from the external ROM. At the next rising clock edge, the ALTPLL_RECONFIG

megafunction asserts the

write_rom_ena

signal and begins placing valid ROM

addresses on the

rom_address_out

port. Assert the

write_from_rom

signal for

1 clock cycle only. This port is available for Stratix III, Stratix IV, Cyclone III,

Cyclone IV, HardCopy III, HardCopy IV, and Arria II GX devices only.

reset_rom_address

No

Resets the ROM address.

When asserted, this signal tells the ALTPLL megafunction to restart the read from

ROM at address 0. Assert the

reset_rom_address

signal for 1 clock cycle only. This

port is available for Stratix III, Stratix IV, Cyclone III, Cyclone IV, HardCopy III,

HardCopy IV, and Arria II GX devices only.

Table 8. ALTPLL_RECONFIG Megafunction Input Ports (Part 3 of 3)

Port Name

Required?

Description