Altera Phase-Locked Loop Reconfiguration IP Core User Manual

Page 4

Page 4

Parameter Settings

Phase-Locked Loop Reconfiguration (ALTPLL_RECONFIG) Megafunction

February 2012

Altera Corporation

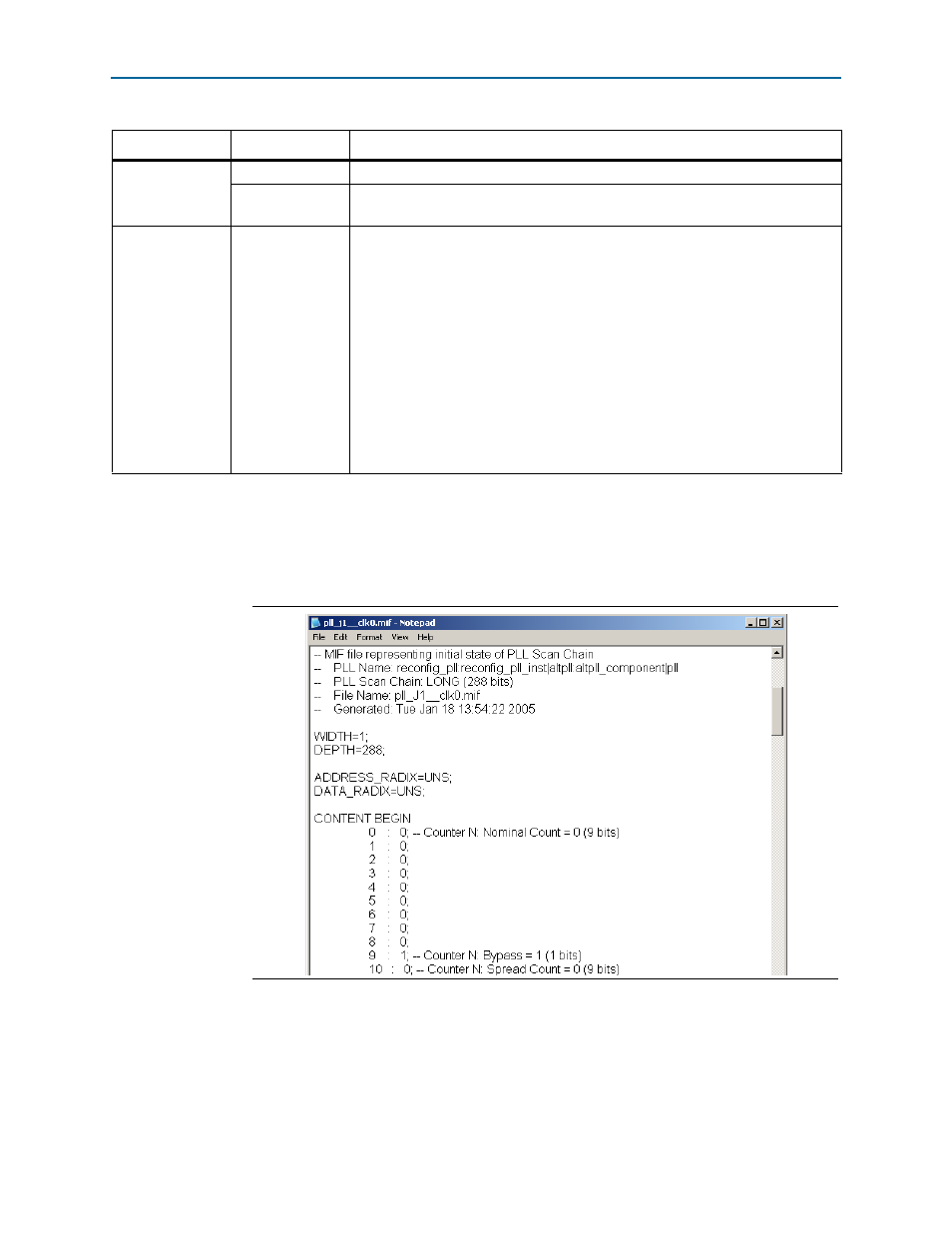

You can open a .mif in a text editor to make use of the comments embedded within

the file. These comments show you the scan chain values and positions based on your

design parameterization (see

). If you open a .mif in the Quartus II software,

you can regenerate the .mif in the ALTPLL parameter editor to restore the comments.

f

For more information about implementing PLL reconfiguration in the supported

Stratix series, refer to

.

EDA

Specifies the libraries needed for functional simulation.

Generate netlist

Specifies whether to turn on the option to generate synthesis area and timing

estimation netlist.

Summary

Specifies the types of files to be generated. A gray checkmark indicates a file that is

automatically generated; a red checkmark indicates an optional file.

Choose from the following types of files:

■

AHDL Include file (

■

VHDL component declaration file (

■

Quartus II symbol file (

■

Instantiation template file (

■

Verilog HDL block box file (

If Generate netlist option is turned on, the file for that netlist is also available

(

Table 1. ALTPLL_RECONFIG Parameter Settings

Page

Options

Description

Figure 1. MIF file