Altera Phase-Locked Loop Reconfiguration IP Core User Manual

Page 46

Page 46

Specifications

Phase-Locked Loop Reconfiguration (ALTPLL_RECONFIG) Megafunction

February 2012

Altera Corporation

lists the

counter_param

settings for Stratix III, Stratix IV, Cyclone III,

Cyclone IV, and Arria II GX devices.

Illegal value

1111

15

Notes to

:

(1) For Stratix III and Stratix IV Top/Bottom PLL, Stratix III and Stratix IV Left/Right PLL, and Cyclone III and

Cyclone IV PLL.

(2) For Stratix III and Stratix IV Top/Bottom PLL, Stratix III and Stratix IV Left/Right PLL, and Arria II GX PLL.

(3) For Stratix III and Stratix IV Top/Bottom PLL only.

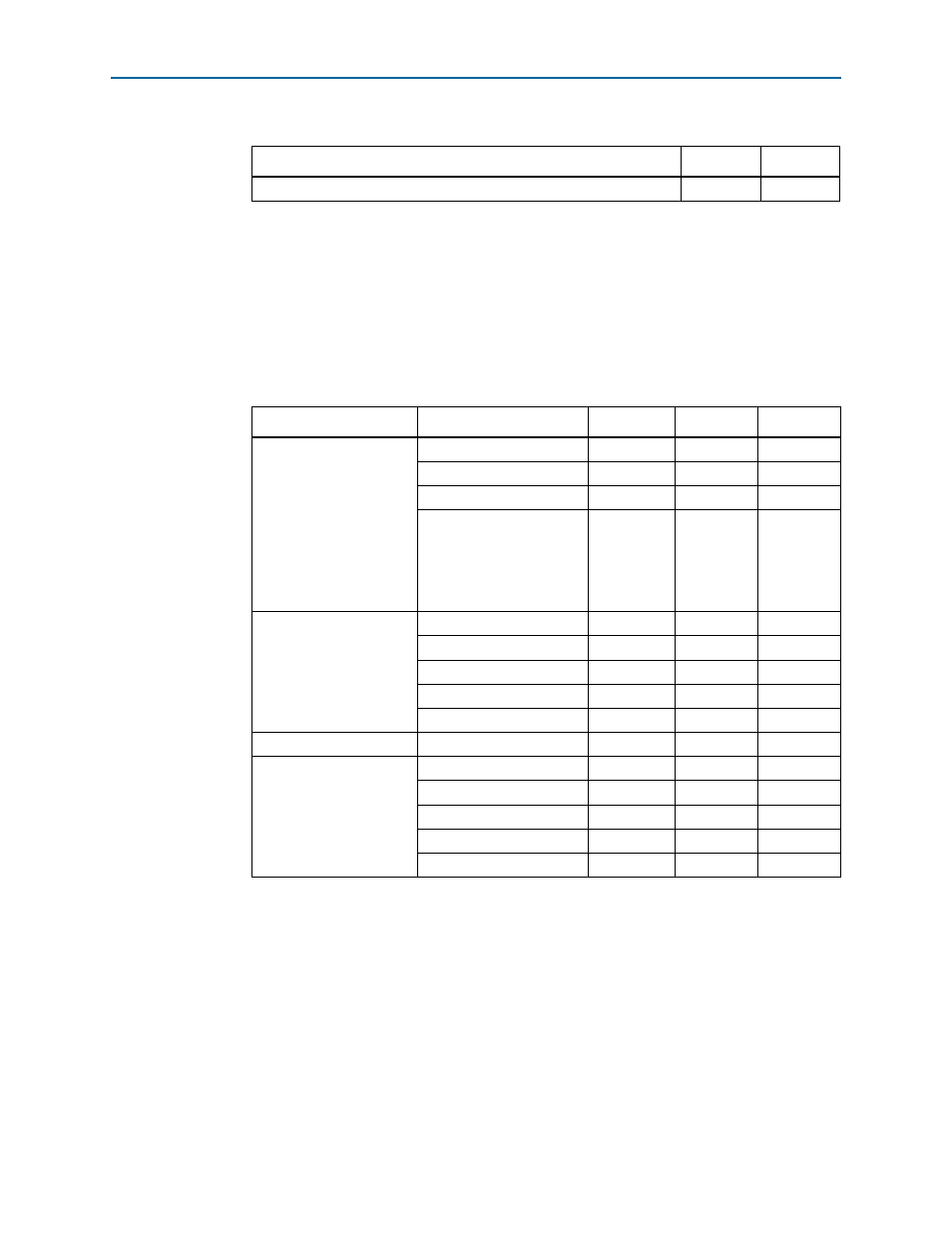

Table 12. counter_param[2..0] Settings for Stratix III, Stratix IV, Cyclone III, Cyclone IV, and

Arria II GX Devices

Counter Type

Counter Param

Binary

Decimal

Width (bits)

Regular counters

C0-C9: Top-Bottom

Stratix III and Stratix IV

C0-C6: Left-Right

Stratix III and Stratix IV

C0-C4: Cyclone III and

Cyclone IV

C0-C6: Arria II GX

High count

000

0

8

Low count

001

1

8

Bypass

100

4

1

Mode (odd/even division)

101

5

1

CP/LF

Charge pump unused

101

5

5

Charge pump current

000

0

3

Loop filter unused

100

4

1

Loop filter resistor

001

1

5

Loop filter capacitance

010

2

2

VCO

VCO Post Scale

000

0

1

M/N Counters

High count

000

0

8

Low count

001

1

8

Bypass

100

4

1

Mode (odd/even division)

101

5

1

Nominal count

111

7

9

Note to

:

(1) For even nominal count, the counter bits are automatically set as follows:

■

high_count

=

Nominalcount

/2

■

low_count

=

Nominalcount

/2

For odd nominal count, the counter bits are automatically set as follows:

■

high_count

= (

Nominalcount

+ 1)/2

■

low_count

=

Nominalcount

-

high_count

■

odd/even division bit = 1

For nominal count = 1, Bypass bit = 1.

Table 11. counter_type[3..0] Settings for Stratix III, Stratix IV, Cyclone III, Cyclone IV, and

Arria II GX Devices (Part 2 of 2)

Counter Selection

Binary

Decimal