Altera Phase-Locked Loop Reconfiguration IP Core User Manual

Page 24

Page 24

Design Example

Phase-Locked Loop Reconfiguration (ALTPLL_RECONFIG) Megafunction

February 2012

Altera Corporation

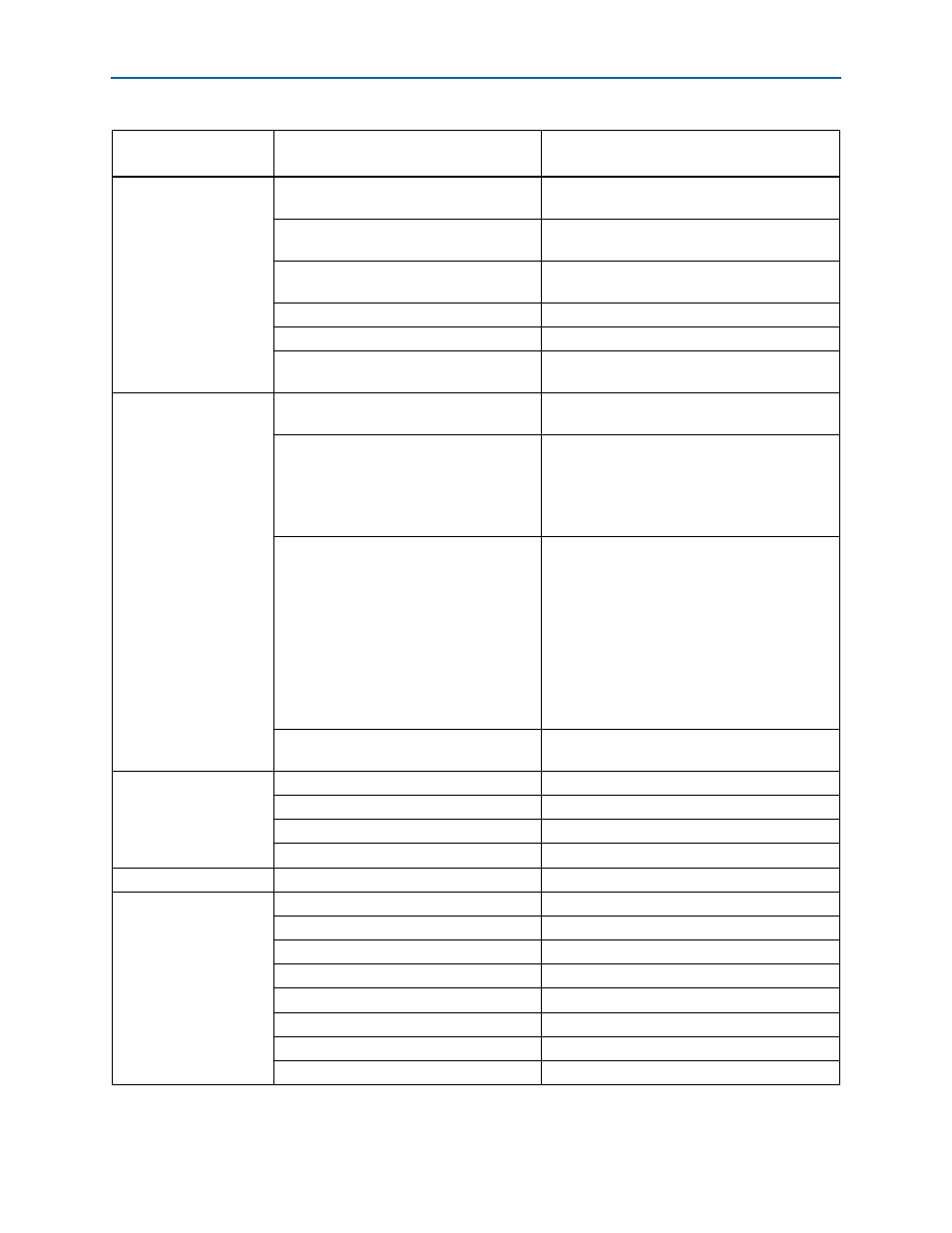

Parameter Settings

(Scan/Inputs/Lock)

Create an ‘pllena’ input to selectively enable

the PLL

Disabled

Create an ‘areset’ input to asynchronously

reset the PLL

Turned on

Create an ‘pfdena’ input to selectively

enable the phase/frequency detector

Turned off

Create ‘locked’ output

Turned on

Enable self reset on loss lock

Turned off

Create output file(s) using ‘Advanced’ PLL

parameters

Turned off

PLL Reconfiguration

Create optional inputs for dynamic

reconfiguration

Turned on

Initial Configuration File (filename)

the_pll_initial.mif—taking an

inclock

of

50 MHz and generating

c0

of 100 MHz

Ensure that this option shows the correct path of

the .mif file before compiling the design to avoid

scan chain mismatch warnings.

Additional Configuration File (filename)

The files are already generated. They are:

■

the_pll_200_mhz.mif—taking an

inclock

of

50 MHz and generating

c0

of 200 MHz

■

the_pll_300_mhz.mif—taking an

inclock

of

50 MHz and generating c0 of 300 MHz

■

the_pll_400_mhz.mif—taking an

inclock

of

50 MHz and generating

c0

of 400 MHz

■

the_pll_500_mhz.mif—taking an

inclock

of

50 MHz and generating

c0

of 500 MHz

Create optional inputs for dynamic phase

reconfiguration

Turned off

Output Clocks

(clk c0)

Use this clock

Turned on

Enter output clock frequency

100 MHz

Clock phase shift

0 degrees

Clock duty cycle (%)

50

EDA

Generate netlist

Turned off

Summary

Variation file

Turned on

PinPlanner ports PPF file

Turned on

AHDL Include file

Turned on

VHDL component declaration file

Turned on

Quartus II symbol file

Turned on

Instantiation template file

Turned on

Verilog HDL block box file

Turned on

Reconfiguration File for altpll_reconfig

Turned on

Table 6. Configuration Settings for the ALTPLL Megafunction (Part 2 of 2)

MegaWizard Plug-In

Manager Page

Settings

Value