Pcie interface – Kontron SMARC-sA3874i User Manual

Page 29

29

www.kontron.com

User’s Guide

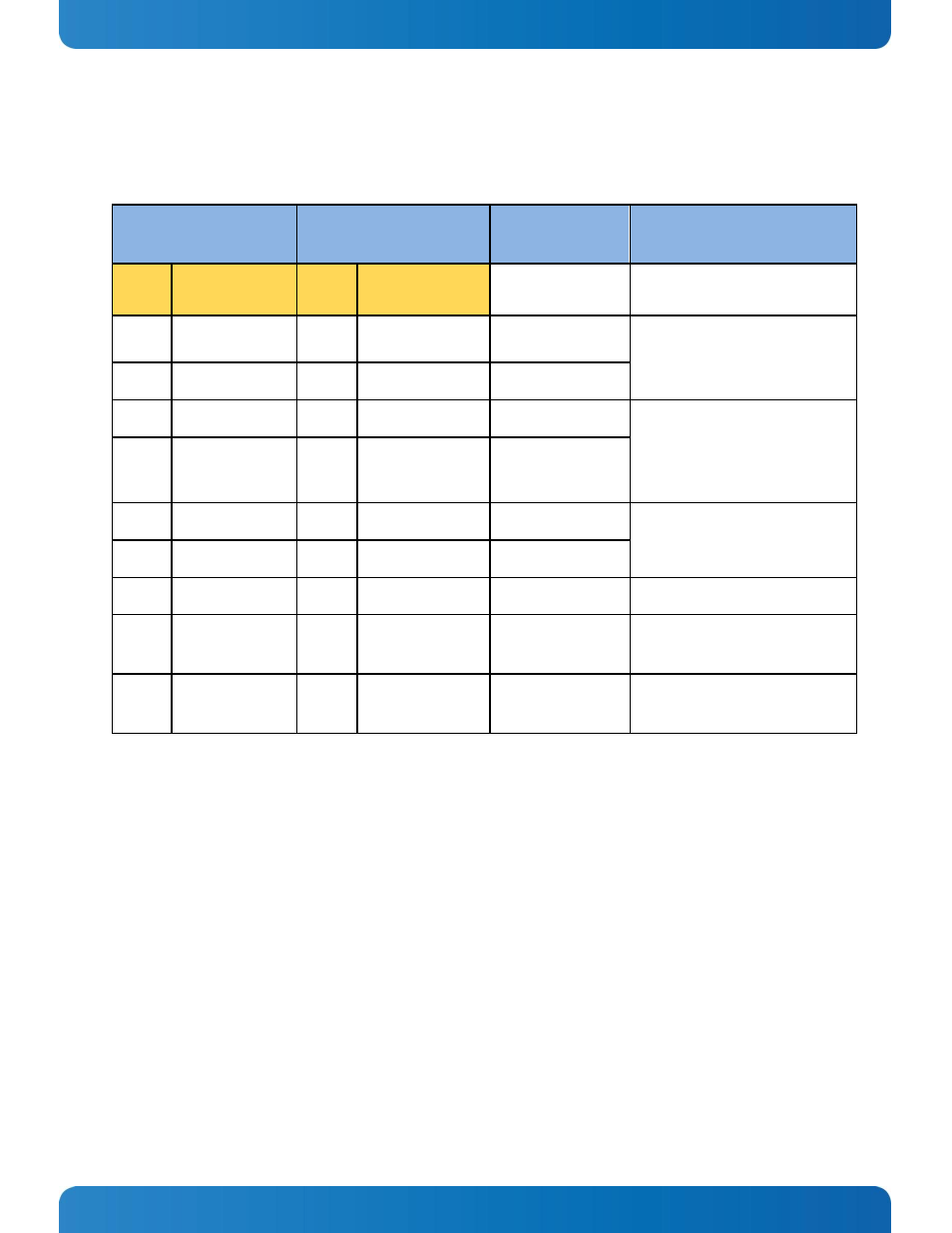

3.2.13 PCIe Interface

The ULP-COM sA3874i module supports one PCIe GEN2 interface. PCIe interface signals are exposed on the ULP-

COM sA8374 edge connector as shown below:

ULP-COM sA3874i Edge

Finger

IT CORTEX A8 CPU

Net Name

Notes

Pin #

Pin Name

Pin #

Pin Name

P89

PCIE_A_TX_P

AD2

PCIE_TXP0

PCIE_A_TX0+

Differential PCIe Link A transmit

data pair 0. Series decoupling

caps are provided in the Module.

P90

PCIE_A_TX_N

AD1

PCIE_TXN0

PCIE_A_TX0-

P86

PCIE_A_RX_P

AC1

PCIE_RXN0

PCIE_A_RX0+

Differential PCIe Link A receive

data pair 0. Series decoupling

caps are not provided in the

Module.

P87

PCIE_A_RX_N

AC2

PCIE_RXP0

PCIE_A_RX0-

P83

PCIE_A_REFCK_P

PCIE_A_REFCK0+

Differential PCIe Link A

reference clock output

P84

PCIE_A_REFCK_N

PCIE_A_REFCK0-

P78

PCIE_A_CKREQ#

PCIE_A_CKREQ#

PCIe Port A clock request input

P74

PCIE_A_PRSNT#

L6

TIM7_IO/GP0[28]

PCIE_A_PRSNT#/PC

IE_A_PRSNT_1V8#

PCIe Port A present input

P75

PCIE_A_RST#

PCIE_A_RST#

PCIe Port A reset output, active

low is generated from CPLD