Lvds serialized lcd display interface, Figure 2: sitara module lvds lcd implementation, 7 lvds serialized lcd display interface – Kontron SMARC-sA3874i User Manual

Page 14

14

www.kontron.com

User’s Guide

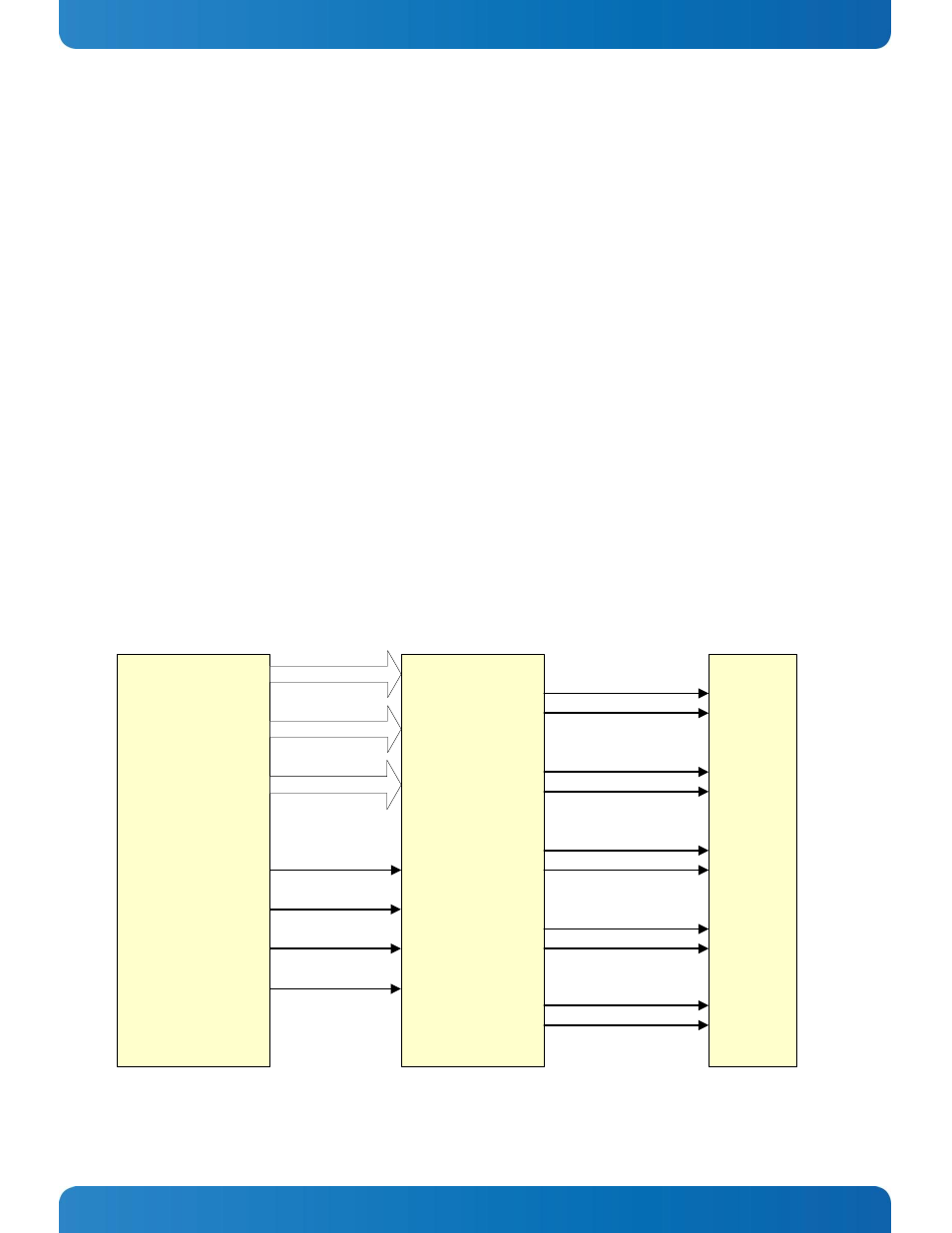

3.2.7 LVDS Serialized LCD Display Interface

The LVDS color packing used on the Module is in the “18 bit color compatible mode” (more details on this can be

found later in this section and in the

Ultra Low Power – Computer On Module Hardware Specification

). The display

connection may be 18 bit or 24 bit, but if a 24 bit connection is used, then the display must be capable of

accepting an “18 bit color packing”. This is sometimes alternatively referred to as “6 bit pack” (it’s 6 bits per

color, or 18 bits total …). For single channel LVDS, a display resolution up to approximately 1280 x 1024 may be

supported (approximate” because factors such as Carrier Board trace lengths, routing quality, cable length and

quality, Carrier EMI and ESD suppression device selections and display timing particulars can affect the maximum

resolution achieved). For high resolution displays (1280 x 1024 and higher), a Carrier Board based dual channel

LVDS transmitter operating from the Module parallel data path should be used instead.

For flat panel use, parallel LCD data and control information (Red, Green and Blue color data, Display Enable,

Vertical Synch and Horizontal Synch) are serialized onto a set of LVDS differential pairs. The information is packed

into frames that are 7 bits long. For 18 bit color depths, the data and control information utilize three LVDS

channels (18 data bits + 3 control bits = 21 bits; hence 3 channels with 7 bit frames) plus a clock pair. For 24 bit

color depths, four LVDS channels are used (24 data bits + 3 control bits + 1 unused bit = 28 bits, or 4 x 7) plus a

clock pair. The LVDS clock is transmitted on a separate LVDS pair. The LVDS clock period is 7 times longer than the

pixel clock period. The LVDS clock edges are off from the 7 bit frame boundaries by 2 pixel periods. Unfortunately,

there are two different 24 bit color mappings in use. The more common one, sometimes referred to as “24 bit

standard color mapping” is not compatible with 18 bit panels, as it places the most significant RGB color data on

the 4

th

LVDS data pair – the pair that is not used on 18 bit panels. There is a less common “24 bit / 18 bit

compatible” mapping that puts the least significant color bits of the 24 bit set onto the 4

th

LVDS pair and allows

24 bit color depths.

Figure 2: Sitara Module LVDS LCD Implementation

E

D

G

E

F

IN

G

E

R

(J

3

)

SITARA CPU

(U7)

LVDS

XMITTER

(U19)

TI

SN65LVDS93AZ

LVDS0+

VOUT0_HSYNC

VOUT0_VSYNC

VOUT0_CLK

AA10

AC11

AB13

AD12

A3

A4

B4

A2

LVDS0-

LVDS1+

LVDS1-

LVDS2+

LVDS2-

LVDS3+

LVDS3-

LVDS_CK+

LVDS_CK-

H2

H1

G2

G1

E2

E1

C2

C1

D2

D1

S125

S126

S128

S129

S131

S132

S137

S138

S134

S135

VOUT0_AVID

VOUT0_B[0:7]

VOUT0_G[0:7]

VOUT0_R[0:7]