Common/synth lane adaptive equalizer registers – Achronix Speedster22i 10G/40G/100G Ethernet User Manual

Page 99

UG029, September 6, 2013

99

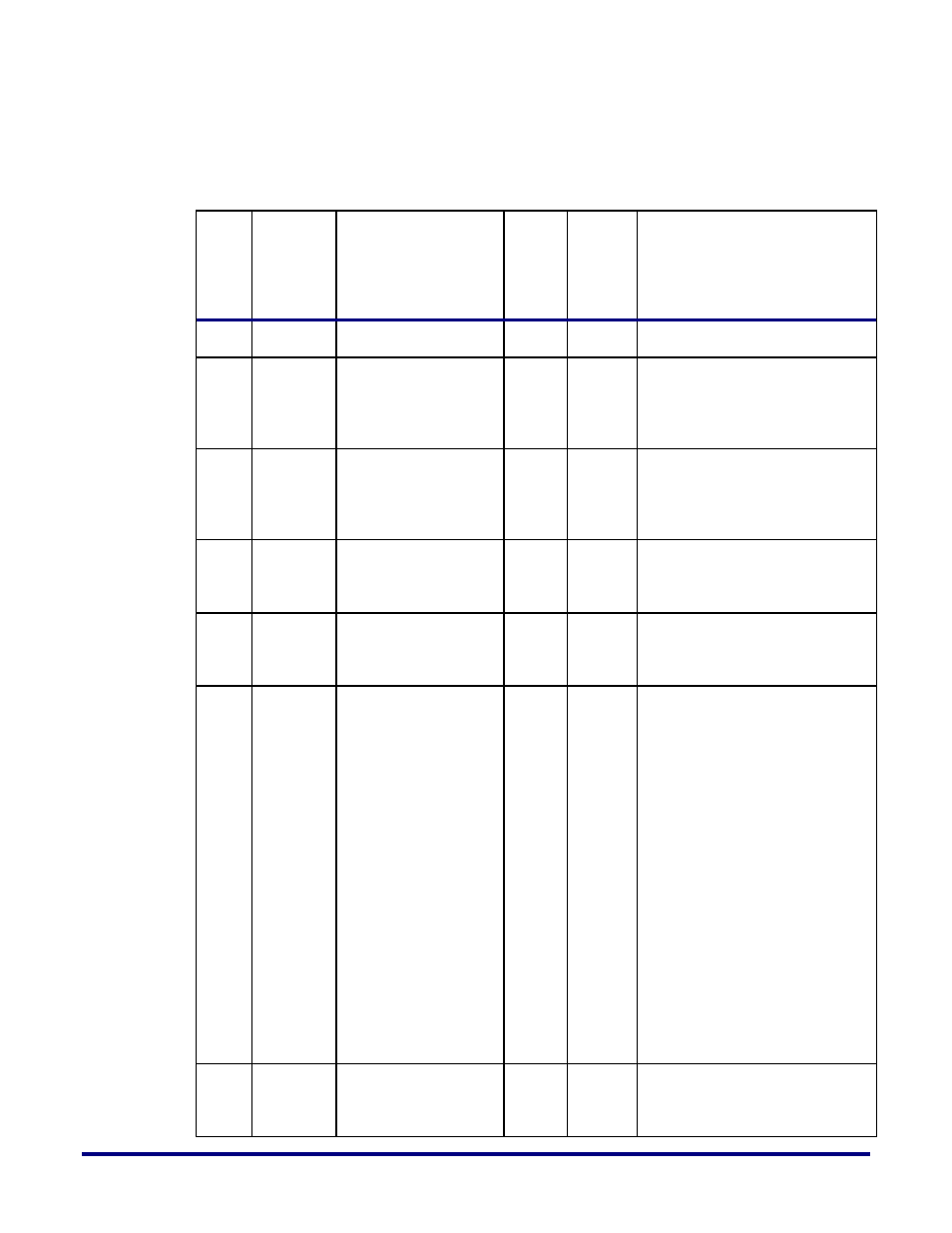

Common/Synth Lane Adaptive Equalizer Registers

Table 63

– Table 6-14: Common/Synth Lane Adaptive Equalizer FSM

Registers

Reg

Pg.

(hex)

Reg

Offset

[Start

Bit: End

Bit]

(hex)

Register Field Name

Reg

Type

RW/R

Default

Value

(hex)

Description

4

8[6:6]

RXEQ_CALEN

RW

1

RX Equalization FSM enable.

Active High

4

21[5:1]

RXEQ_COARSE_ST

EP

RW

2

RX Equalization calibration

coarse mode step size. When

swept, each variable starts from

0, and is increased by this value

until saturated.

4

23[5:1]

RXEQ_FINE_STEP

RW

1

RX Equalization calibration fine

mode step size. When swept,

each variable starts from 0, and

is increased by this value until

saturated.

4

25[2:0]

RXEQ_LOOKUP_LA

STCODE

RW

7F

RX Equalization calibration

lookup table last code control.

Specifies the last lookup code in

the table to be used.

4

1E[6:0]

RXEQ_COARSE_IT

ER_NUM

RW

2

Equalization calibration course

iteration count control. Sets the

number of iterations performed

during coarse mode.

4

20[7:0]

21[7:7]

RXEQ_COARSE_RU

N_MASK

RW

1FD

Equalization calibration course

mode variable control mask.

Each bit controls whether or not

an equalization variable will be

swept during coarse mode.

0 - Do not sweep variable

1 - Sweep variable

Bit 0 - AGC low frequency gain

Bit 1 - AGC high frequency gain

Bit 2 - AGC AC Boost

Bit 3 - Pulse-shaping DFE 3dB

cut-off frequency

Bit 4 - Pulse-shaping DFE gain

Bit 5 - Discontinuity DFE N-1

tap gain

Bit 6 - Discontinuity DFE N-2

tap gain

Bit 7 - Discontinuity DFE N-3

tap gain

Bit 8 - Discontinuity DFE N-4

tap gain

4

1F[6:0]

RXEQ_FINE_ITER_

NUM

RW

4

Equalization calibration fine

iteration count control. Sets the

number of iterations performed

during fine mode.