Auto-negotiation registers – Achronix Speedster22i 10G/40G/100G Ethernet User Manual

Page 86

86

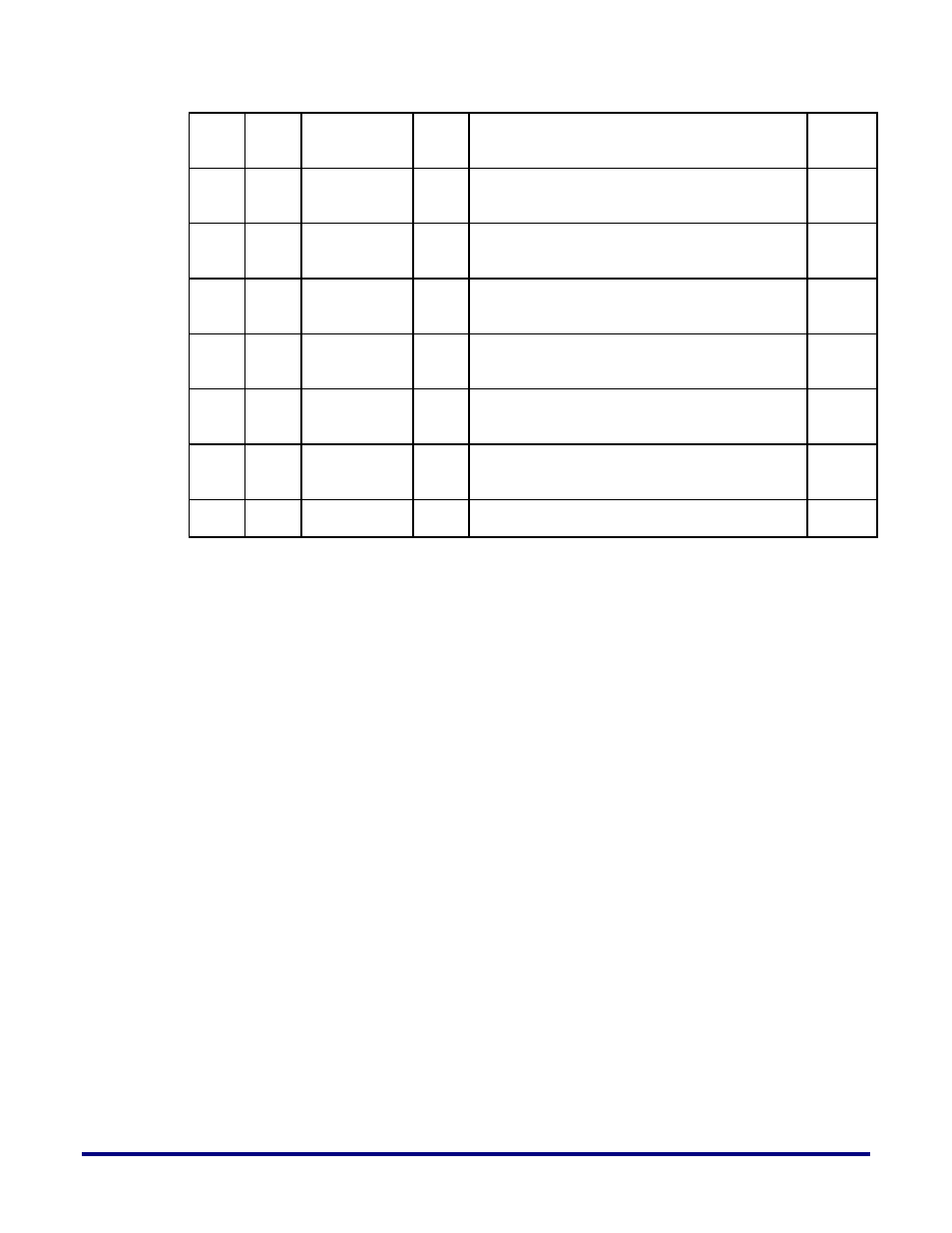

UG029, September 6, 2013

123

1EC

LANE MAP

13

RO

4:0: Lane mapping register for PCS lane 13

15:5: reserved

Note: Bits 15:0 are reserved for 40GBASE-R.

0

124

1F0

LANE MAP

14

RO

4:0: Lane mapping register for PCS lane 14

15:5: reserved

Note: Bits 15:0 are reserved for 40GBASE-R.

0

125

1F4

LANE MAP

15

RO

4:0: Lane mapping register for PCS lane 15

15:5: reserved

Note: Bits 15:0 are reserved for 40GBASE-R.

0

126

1F8

LANE MAP

16

RO

4:0: Lane mapping register for PCS lane 16

15:5: reserved

Note: Bits 15:0 are reserved for 40GBASE-R.

0

127

1FC

LANE MAP

17

RO

4:0: Lane mapping register for PCS lane 17

15:5: reserved

Note: Bits 15:0 are reserved for 40GBASE-R.

0

128

200

LANE MAP

18

RO

4:0: Lane mapping register for PCS lane 18

15:5: reserved

Note: Bits 15:0 are reserved for 40GBASE-R.

0

129

204

LANE MAP

19

RO

4:0: Lane mapping register for PCS lane 19

15:5: reserved

Note: Bits 15:0 are reserved for 40GBASE-R.

0

130 -

255

208 -

3FC

Reserved

0