Implementation with ace, Software/hardware requirements, Creating an ethernet instance – Achronix Speedster22i 10G/40G/100G Ethernet User Manual

Page 21: Configuring the 10/40/100g ethernet core

UG029, September 6, 2013

21

Implementation with ACE

Software/Hardware Requirements

The ACE software suite has the following system requirements:

Platform:

o 64 bit Linux (RHEL/Centos)

o 64bit Windows 7

Memory Requirements by design size:

o Minimum: 12GB

o Recommended for < 100k LUTs: 16GB

o Recommended for 100k – 400k LUTs: 24GB

o

Recommended for > 400k LUTs: 32GB

Creating an Ethernet Instance

The ACE design suite documentation outlines how to install the software, launch it, and

setup your first project. Refer to ACE documentation to learn how to setup your first project.

Configuring the 10/40/100G Ethernet Core

The 10/40/100G Ethernet core is automatically generated from a design wizard in the ACE

design tool suite. Simply launch the IP wizard, select the 10/40/100G Ethernet core from the

list of available IP and a configuration wizard will prompt the user for configuration options.

The options that are presented will be based on the number of lanes you chose and the speed

of each lane. Only certain combinations are available and the wizard will restrict the user to

only those 5 modes available:

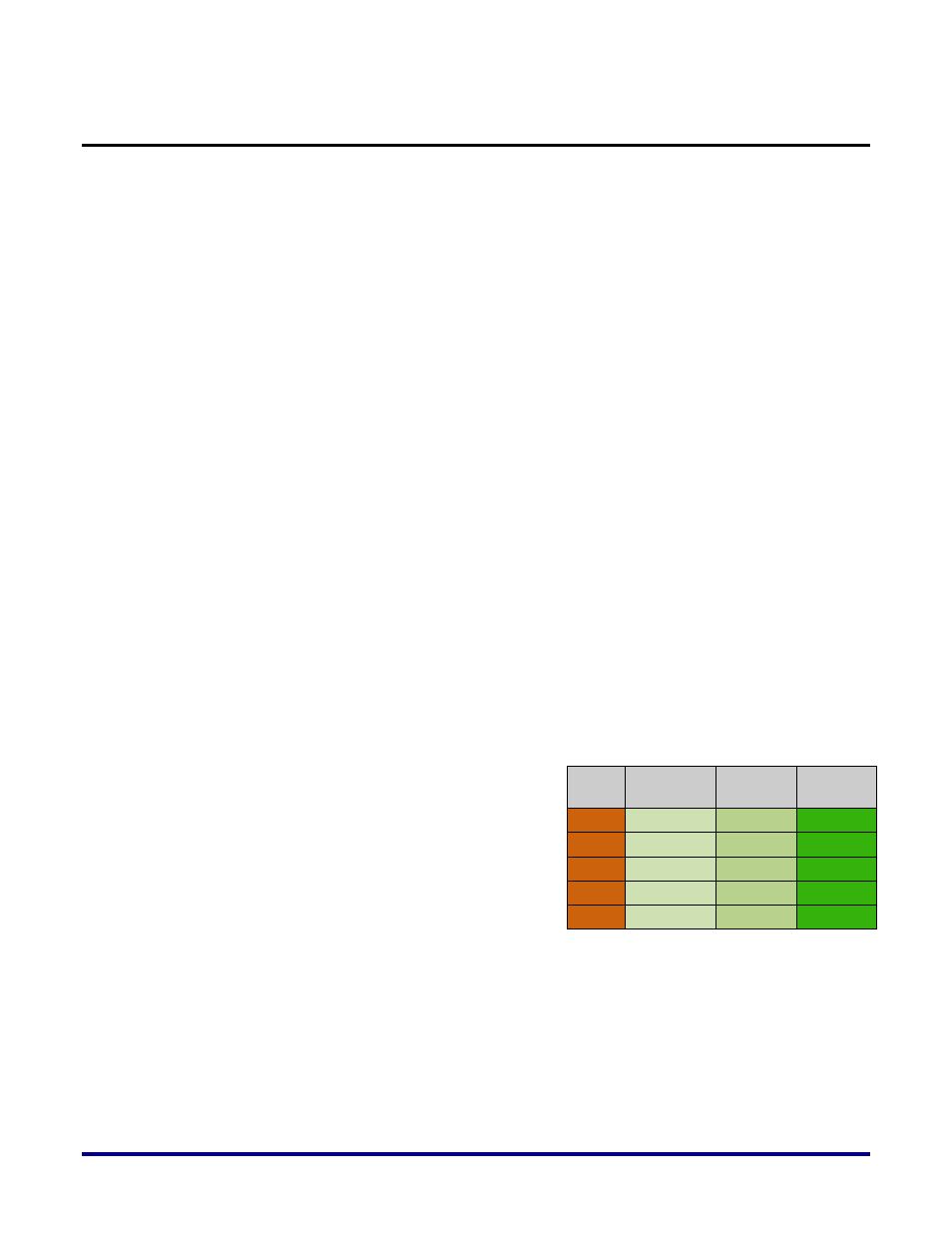

Table 12

– Five modes of operation

Mode

10G

Channels

40G

Channels

100G

Channels

1

12

0

0

2

2

0

1

3

0

3

0

4

4

2

0

5

8

1

0

The Speedster22i 10/40/100G Ethernet MAC IP wizard configuration menu is shown below.

The “Target Device” is selected by the user from a series of drop-down menus that will limit

the options in successive option choices. If we were to select zero 100G lanes we could select

two 40G and four 10G lanes. These options are bound by the five modes of operation defined

above.

Once the lane configuration are chosen, the user will need to define the clock speeds for the

reference clock, serial bus interface clock; and the transmit and receive clock for the lane

groups. Groups of four lanes share a common clock source.