Achronix Speedster22i 10G/40G/100G Ethernet User Manual

Page 72

72

UG029, September 6, 2013

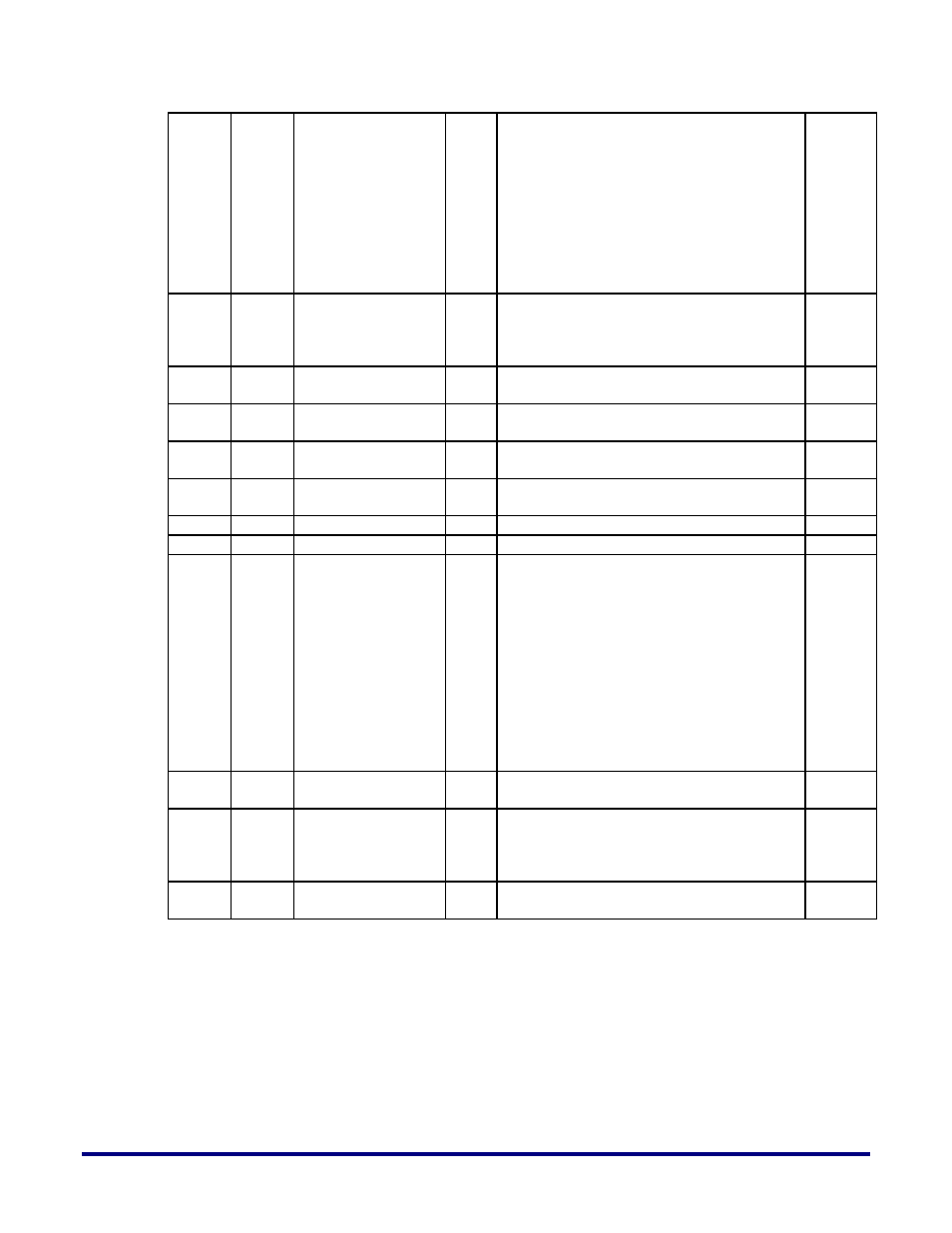

5

314

PARTNER_ABILIT

Y

RO

Received ability from remote device after

auto-negotiation has completed.

Depending on the mode of operation, the

bit definitions are shown in Table 39

(SGMII PCS)

DEVICE/PARTNER_ABILITY Register

Description - 1000Base-X mode on page

74 and Table 39

– (SGMII PCS)

DEVICE/PARTNER_ABILITY Register

Description - SGMII Mode on page 74

0

6

318

AN_EXPANSION

ROR

reserved

Bit 0: real-time page receive indication

Bit 1: latched high page received

indication (cleared on read)

0

7

31c

DEVICE_NP

RO

The PCS does not support next page

auto-negotiation.

0

8

320

PARTNER_NP

RO

The PCS does not support next page

autonegotiation.

0

9:14

324:3

38

RO

reserved

0

15

33c

EXTENDED_STAT

US

RO

The PCS does not support extended

status, always 0.

16

340

reserved

RO

17

344

reserved

RO

18

348

LINK_TIMER_lo

RW

Auto Negotiation Link Timer (RW). Set the

Link Timer value from 0 to 16ms in 8ns

steps (125MHz clock periods). The reset

value sets the Link Timer to 10ms

(1250000).

Bits 15:0 are stored in the _lo register.

Bits 20:16 are stored in the _hi register

bits 4:0.

Unused bits are reserved and set to read

only value 0.

Bit 0 is unused (i.e. value in steps of 2

only) and always 0.

0x12d0

19

34c

LINK_TIMER_hi

RW

Bits 20:16 of the timer value are stored in

bits 4:0.

0x13

20

350

IF_MODE

RW

SGMII enable and mode configuration.

Used to set the PCS interface operation.

See Table 42

– (SGMII PCS) IF_MODE

Register Description on page 76

0

21:31

354:3

7C

reserved

RO

unused