Pma adaptive equalizer registers, Tx/rx lane adaptive equalizer registers – Achronix Speedster22i 10G/40G/100G Ethernet User Manual

Page 98

98

UG029, September 6, 2013

is not used if

PCIEMODE_SEL=0.

4

1A[5:4]

CMNTXPIPE_TXDR

VSLEW_GEN3

RW

0

TX IO driver slew-rate look-up

table entry for PCIE Gen3 If

PCIEMODE_SEL=1. This value

is used if PCIEMODE_SEL=0.

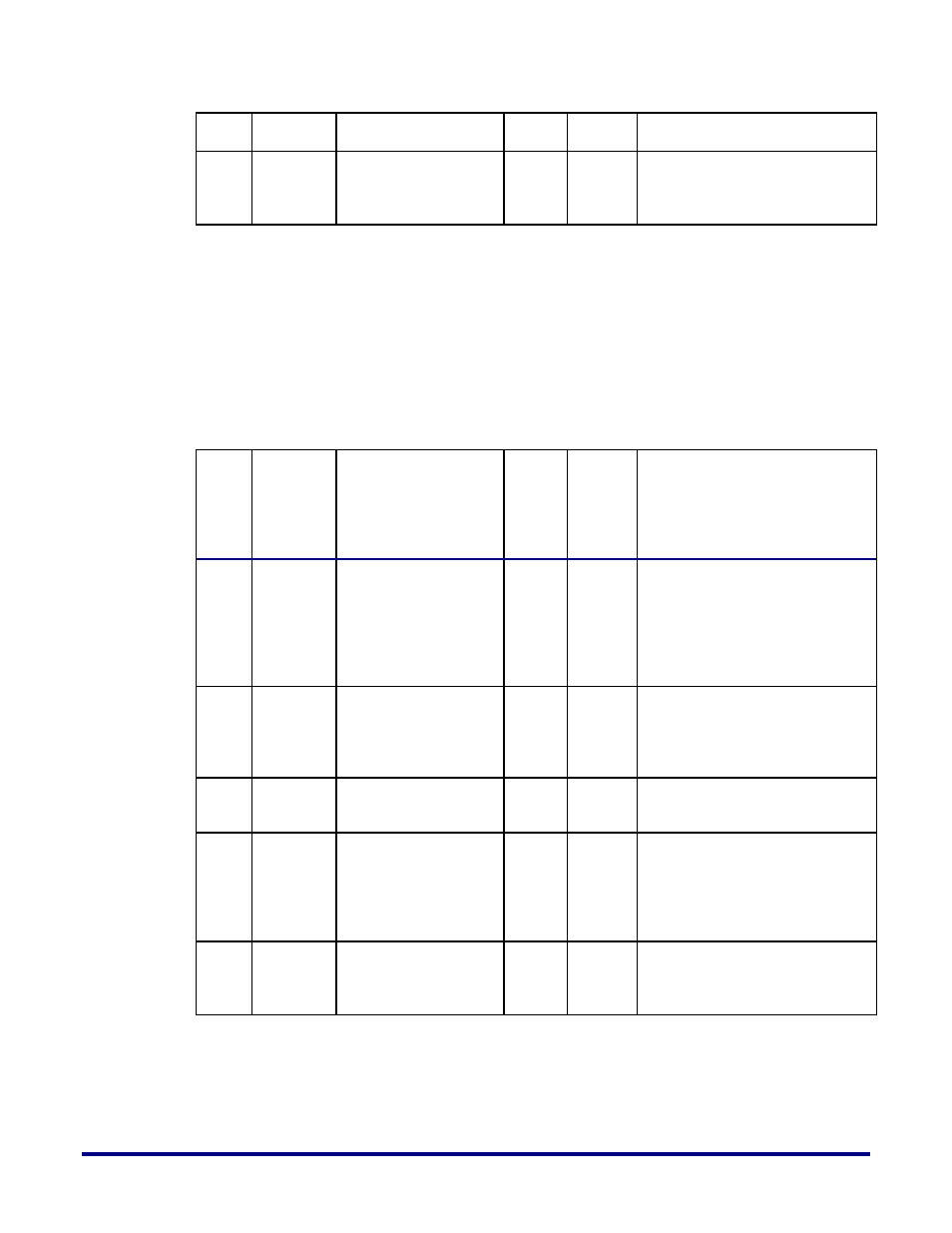

PMA Adaptive Equalizer Registers

The following sections describe registers used to configure the Adaptive Equalization within

the PHY. The Receiver/Transmitter and Synthesizer control registers are split into the two

sub-sections.

TX/RX Lane Adaptive Equalizer Registers

Table 62

– TX/RX Lane Adaptive Equalizer FSM Registers

Reg

Pg.

(hex)

Reg

Offset

[Start

Bit: End

Bit]

(hex)

Register Field Name

Reg

Type

RW/R

Default

Value

(hex)

Description

0

1C[2:0]

PCSRXEQ_PRECAL

_CODE_SEL

RW

0

Provides a RX Equalizer Pre-

Hint, prior to beginning adaptive

equalization Please refer to

Datasheet for a description of

what backplane ranges the RX-

Hint values are intended to

support

0

1F[0:0]

PCSRXEQ_START

RW

0

Enables adaptive RX

equalization 0 - Disables

adaptive RX equalization 1 -

Enables adaptive RX

equalization

0

55[6:6]

PCSRXEQ_LOCWR

EN

RW

1

RX Equalizer control

(PCSRXEQ_*) override enable.

Active Low

0

1D[7:0]

1E[5:0]

RXEQ_BEST_EYE_

VAL

RW

0

Optimum Receive Eye value.

Safe for sampling when

_DONE_ signal has asserted:

14'h0000

– Completely Closed

Eye 14'hFFFF

– Completely

Open Eye

0

26[3:3]

RXEQ_DONE

RW

0

0

– RX EQ calibration not

completed

1

– RX EQ calibration

completed