Achronix Speedster22i 10G/40G/100G Ethernet User Manual

Page 83

UG029, September 6, 2013

83

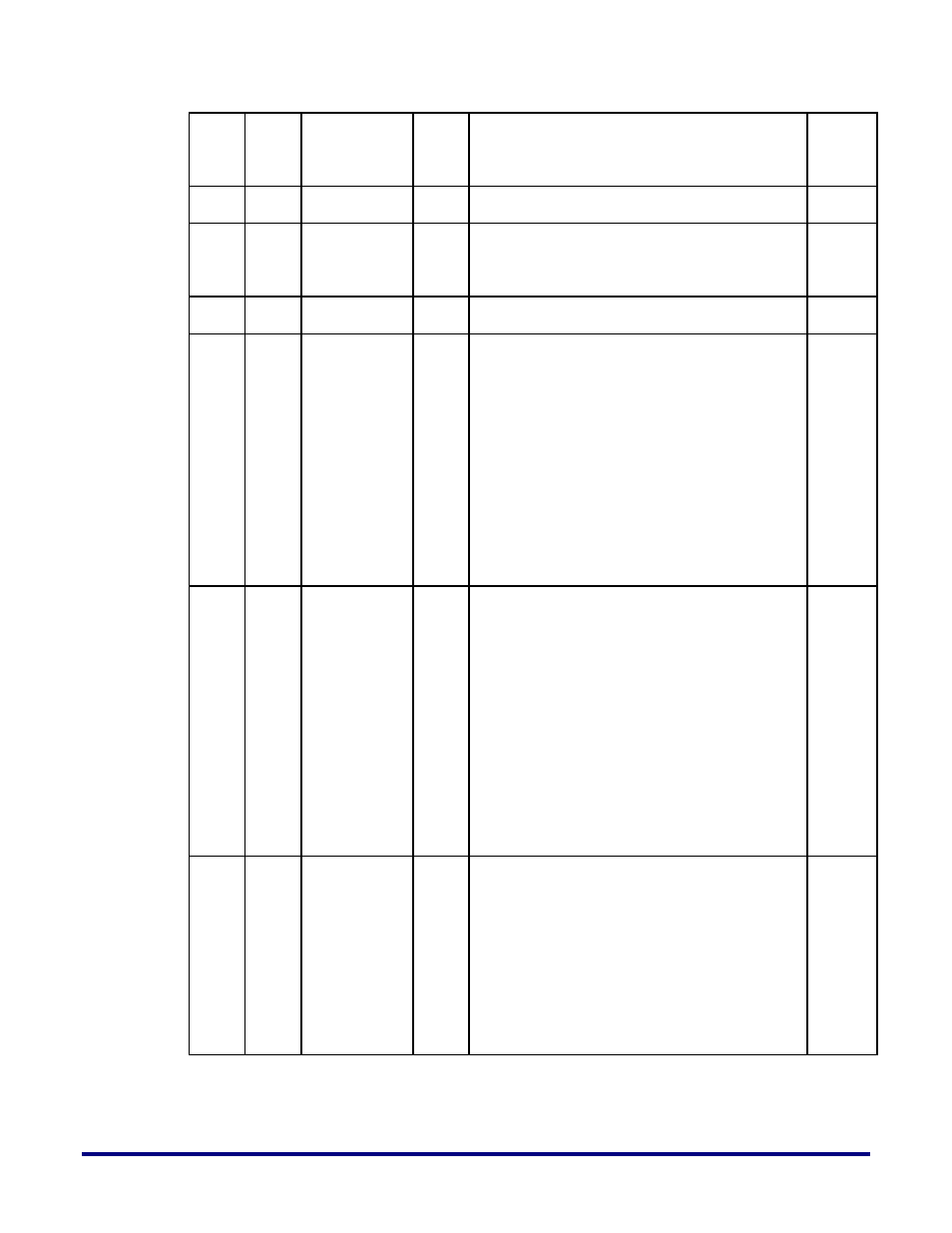

43

AC

10/40/100G

BASE-R

TEST ERR

CNT

ROR

Test-pattern error counter. (NR)

0

44

B0

BER HIGH

ORDER CNT

RO

15:0: Bits 21:6 of BER counter. (NR)

0

45

B4

ERR BLK

HIGH

ORDER CNT

RO

15: High order counter present. Always 1,

writes ignored.

14: Reserved. Always 0, writes ignored.

13:0: Bits 21:8 of errored blocks counter. (NR)

0

46-

49

B8-

C4

Reserved

0

50

C8

MULTI-LANE

ALIGN

STATUS 1

RO

15:13: Reserved

12: Lane alignment status. 1=All Receive

lanes locked and aligned.

11:8: Reserved

7: Lane 7 block lock

6: Lane 6 block lock

5: Lane 5 block lock

4: Lane 4 block lock

3: Lane 3 block lock

2: Lane 2 block lock

1: Lane 1 block lock

0: Lane 0 block lock

Note: Bits 7:4 are reserved for 40GBASE-R.

0

51

CC

MULTI-LANE

ALIGN

STATUS 2

RO

15:12: Reserved

11: Lane 19 block lock

10: Lane 18 block lock

9: Lane 17 block lock

8: Lane 16 block lock

7: Lane 15 block lock

6: Lane 14 block lock

5: Lane 13 block lock

4: Lane 12 block lock

3: Lane 11 block lock

2: Lane 10 block lock

1: Lane 9 block lock

0: Lane 8 block lock

Note: Bits 11:0 are reserved for 40GBASE-R.

0

52

D0

MULTI-LANE

ALIGN

STATUS 3

RO

15:8: Reserved

7: Lane 7 alignment marker lock

6: Lane 6 alignment marker lock

5: Lane 5 alignment marker lock

4: Lane 4 alignment marker lock

3: Lane 3 alignment marker lock

2: Lane 2 alignment marker lock

1: Lane 1 alignment marker lock

0: Lane 0 alignment marker lock

Note: Bits 7:4 are reserved for 40GBASE-R.

0