Achronix Speedster22i 10G/40G/100G Ethernet User Manual

Page 52

52

UG029, September 6, 2013

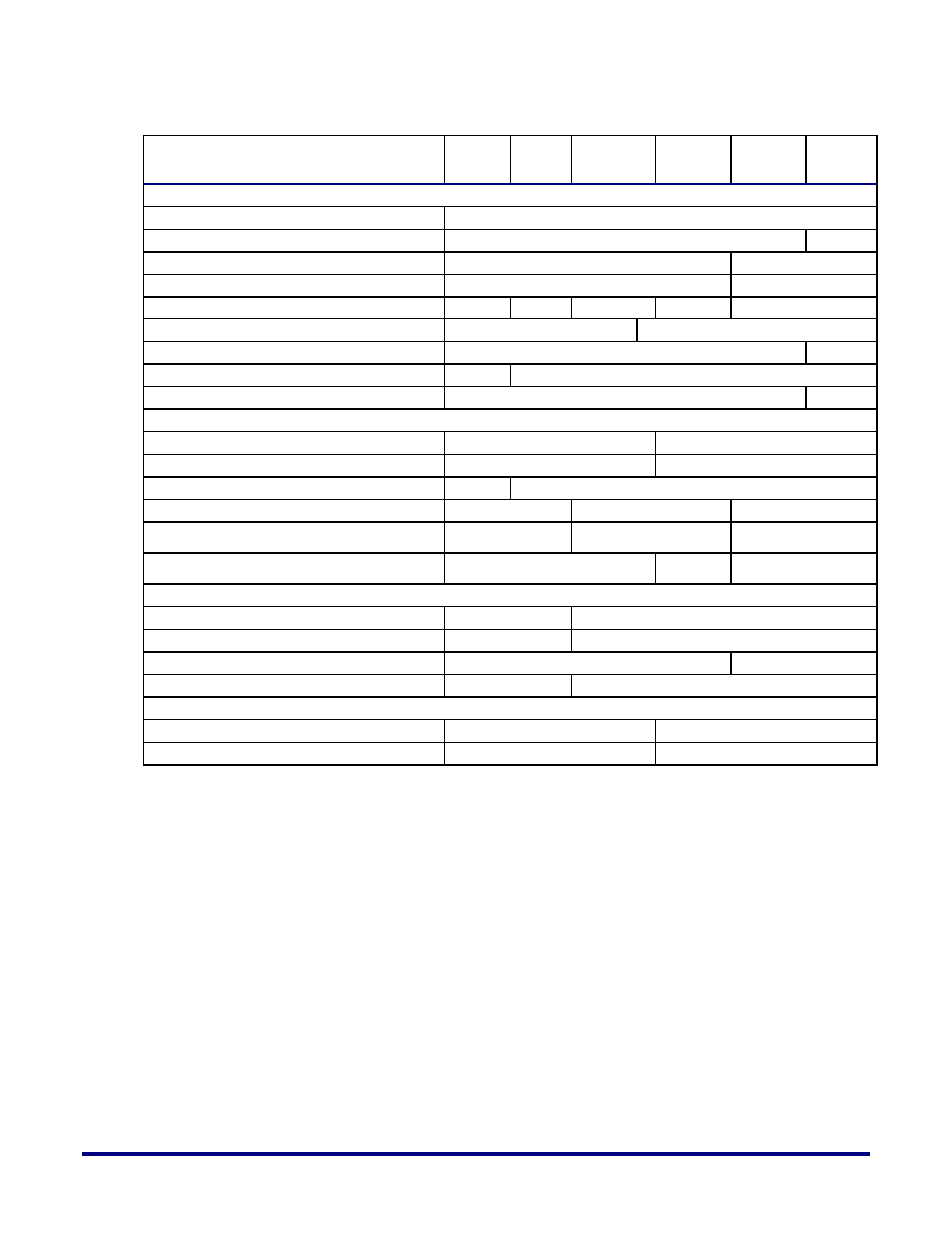

Table 28

– Overview of PMA Behavior During the Various Power States

IO Pin Signal

P0

P0s

P1

P2

Power

Down

Hard

Reset

Power State Controls and Status

IRST_PCS_POR_B_A

1’b1

IRST_PCS_HARD_TXRX_Lx_B_A

1’b1

1’b0

IPD_PCS_[TX,RX]_Lx_B

1’b1

1’b0

IPD_PCS_SYNTH_B

1’b1

1’b0

ICTL_PCS_PSTATE_Lx_[1:0]

2’b00

2’b01

2’b10

2’b11

2’b??

OCTL_PCS_[TX,RX]_READY_Lx_A

1’b1

1’b0

OCTL_PCS_[TX,RX]_STATUS_Lx_A

1’b1

1’b0

OCTL_PCS_SYNTH_READY_A

1’b1

1’b0

OCTL_PCS_SYNTH_STATUS_A

1’b1

1’b0

Transmit Lane Controls and Status

OCK_PCS_TXWORD_PMA_Lx

TX Byte Clock

Keepalive

ICK_PCS_TXWORD_Lx

TX Byte Clock

Keepalive

IDAT_PCS_TXWORD_Lx_[X:0]

Active

5’h00000

ICTL_PCS_TXDETECTRXREQ_Lx_A

1’b0

Depends on Interface

1’b0

OCTL_PCS_TXDETECTRXSTAT_Lx_A

1’b0

Depends on Receiver

Detection Results

1’b0

ICTL_PCS_TXBEACON_Lx_A

1’b0

Depends on

Interface

1’b0

Receive Lane Controls and Status

OCK_PCS_RXWORD_Lx

RX Byte Clock

Keepalive

ODAT_PCS_RX[A,B]WORD_Lx_[X:0]

Recovered Data

5’h00000

OCTL_PCS_RXSIGNALDETEC_Lx_A

Depends on Far End

1’b0

OCTL_PCS_RXCDRLOCK2DATA_Lx_A

Depends on Far End

1’b0

Output Clocks

OCK_PCS_POSTDIV

Postdiv Clock

Keepalive

OCK_PCS_REF

Reference Clock

Keepalive