Achronix Speedster22i 10G/40G/100G Ethernet User Manual

Page 80

80

UG029, September 6, 2013

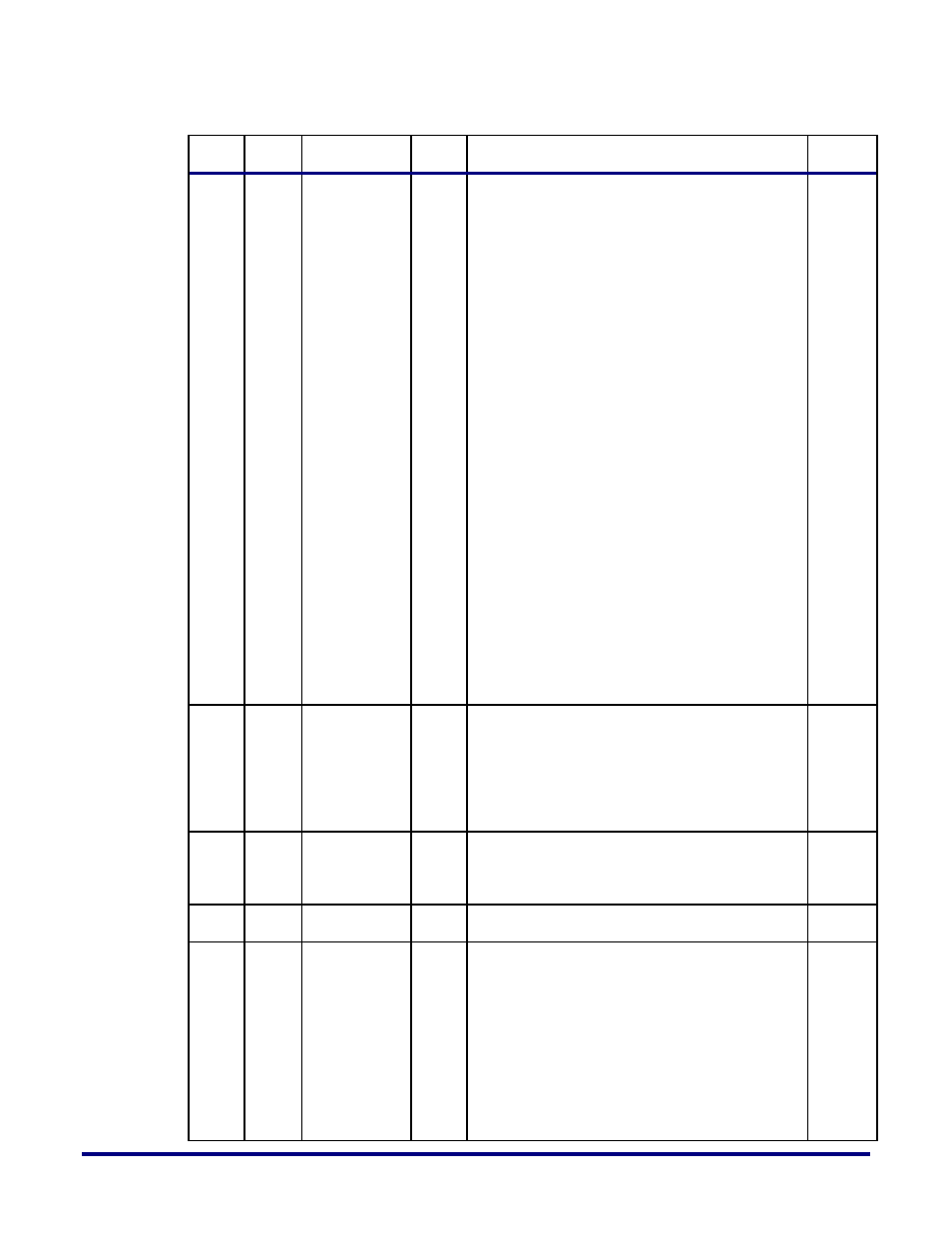

Table 45

– PCS Register Map – General PCS Information

Reg#

Add.

(hex)

Register

Name

Type

Description

Reset

0

00

CONTROL 1

RW

[15]: Reset. 1=PCS reset (see

PCS Reset on page 28), 0=normal

operation. (SC)

[14]: Loopback. 1=Enable loopback (see ),

0=normal.

[13]: Speed selection. (13,6)=11=bits 5:2

select speed.

[12]: Reserved. Always 0, writes ignored.

[11]: Low power. 1=Low power mode,

0=normal.

[10:7]: Reserved. Always 0, writes ignored.

[6]: Speed selection. (13,6)=11=bits 5:2 select

speed.

[5:2]: Speed selection.

0100: 100 Gb/s

0011: 40 Gb/s

0010: Reserved for 802.3av

0001: 10PASS-TS/2BASE-TL

0000: 10 Gb/s

[1:0]: Reserved. Always 0, writes ignored.

Notes:

Only bits 15,14 are writeable. All others are

read-only.

Speed Bits (13,6:2) are set to 110100 for

100GBASE-R, 110011 for 40GBASE-R, or

110000 for 10GBASE-R inherited from global

configuration.

Low Power Bit 11 is not supported, always 0.

0x2040

1

04

STATUS 1

RO

[15:8]: Reserved

[7]: Fault detected. (Not available, always 0)

[6:3]: Reserved

[2]: Receive link status. 1=Link up, 0=link

down. (LL)

[1]: Low power ability. not available, always 0.

[0]: Reserved

0

2

08

DEVICE ID0

RO

Bits 15:0 of Device Identifier

Bits 3..0 are used and set identically to the

segment number of the PCS. All other bits are

0.

n

3

0C

DEVICE ID1

RO

Bits 31:16 of Device Identifier

Always 0.

0

4

10

SPEED

ABILITY

RO

15:9 Reserved

8: 100G capable

7: 40G capable

6:2: Reserved

1: 10PASS-TS/2BASE-TL capable

0: 10G capable

Note: Only bit 8 is set for 100GBASE-R, only

bit 7 is set for 40GBASE-R, and only bit 0 is

set for 10GBASE-R, inherited from global

configuration.

0x0001