1000base-x/sgmii pcs registers description, Table 37, Table 38 – Achronix Speedster22i 10G/40G/100G Ethernet User Manual

Page 73

UG029, September 6, 2013

73

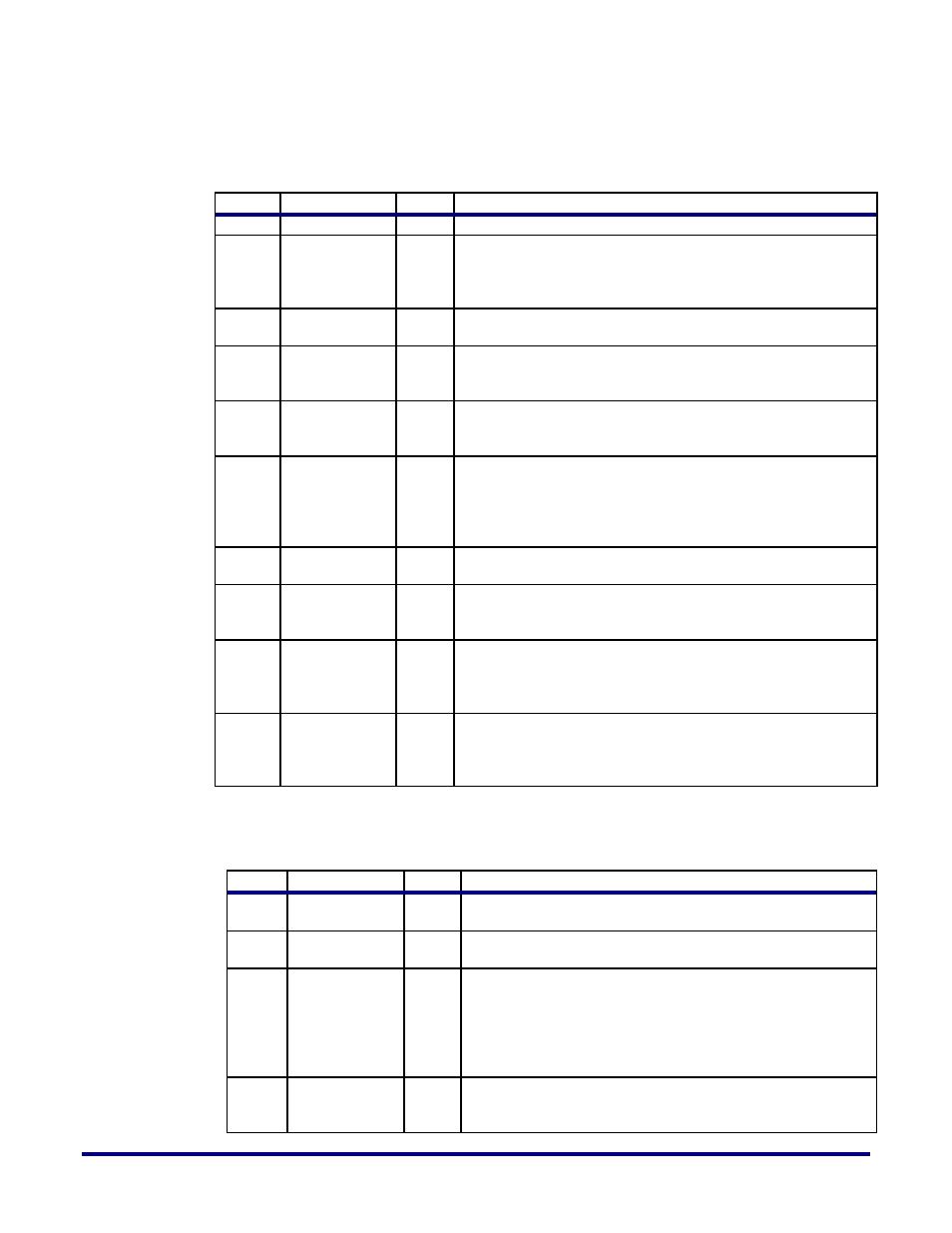

1000Base-X/SGMII PCS Registers Description

Table 37

– (SGMII PCS) CONTROL Register Description

Bit(s)

Name

Type

Description

0 to 5

Reserved

RO

Read only bit always set to ‘0’.

6 and

13

Speed

Selection

RO

Read only bits that define that the PCS only operates in

Gigabit mode:

Bit 13 set to ‘0’.

Bit 6 set to ‘1’.

7

Collision Test

RO

Half duplex not supported by the PCS, read only bit set to

‘0’.

8

Duplex Mode

RO

Read only bit always set to ‘1’ to indication that the PCS

only supports Full Duplex mode of operation and does not

support Half Duplex mode of operation.

9

Restart Auto

Negotiation

RW

Self-

clearing command bit: Set to ‘1’ to restart an auto

negotiation sequence. Set to ‘0’ (Reset value) in normal

operation mode.

10

Isolate

RW

When set to ‘1’, the PCS is isolated from the MAC Layer

device. Should be set to ‘0’ (Reset value) to enable normal

operation.

Note: When set keeps the PCS in reset (equals bit15=1

permanently).

11

Power Down

RW

When set to ‘1’, the PCS drives its powerdown output pin.

setting not relevant, function not used.

12

Auto

Negotiation

Enable

RW

When set to ‘1’ (Reset value) Auto Negotiation is enabled,

set to ‘0’ to disable Auto Negotiation.

14

Loopback

RW

PHY Loopback Command Register. When set to ‘1’, a

serial loopback is implemented in the PMA. Should be set

to ‘0’ (Reset value) during normal operation.

setting not relevant, function not used.

15

Reset

RW

Self-

Clearing Reset Command Register. When set to ‘1’, a

synchronous reset pulse is generated which resets all the

PCS state machines, the Comma detection function, and

the 8b/10b coder / decoder? ‘0’ for normal operation.

Table 38

– (SGMII PCS) STATUS Register Description

Bit(s)

Name

Type

Description

0

Extended

Capability

RO

Read Only bit set to ‘1’ to indicate that the PCS supports

extended registers.

1

Jabber Detect

RO

Read Only bit always set to ‘0’, the PCS does not support

the optional Jabber detection function.

2

Link Status

RO

(LL)

Read Only Link Status Register. When read as a logic

one, indicates that the PCS has determined that a valid

link has been established. When read as a logic zero,

indicates that the link is not valid.

If the link synchronization is lost a ‘0’ is latched which is

cleared only after a register read access.

3

Auto

Negotiation

Ability

RO

Read Only Bit set to ‘1’ to indicate that the PCS PCS

supports Auto-Negotiation.