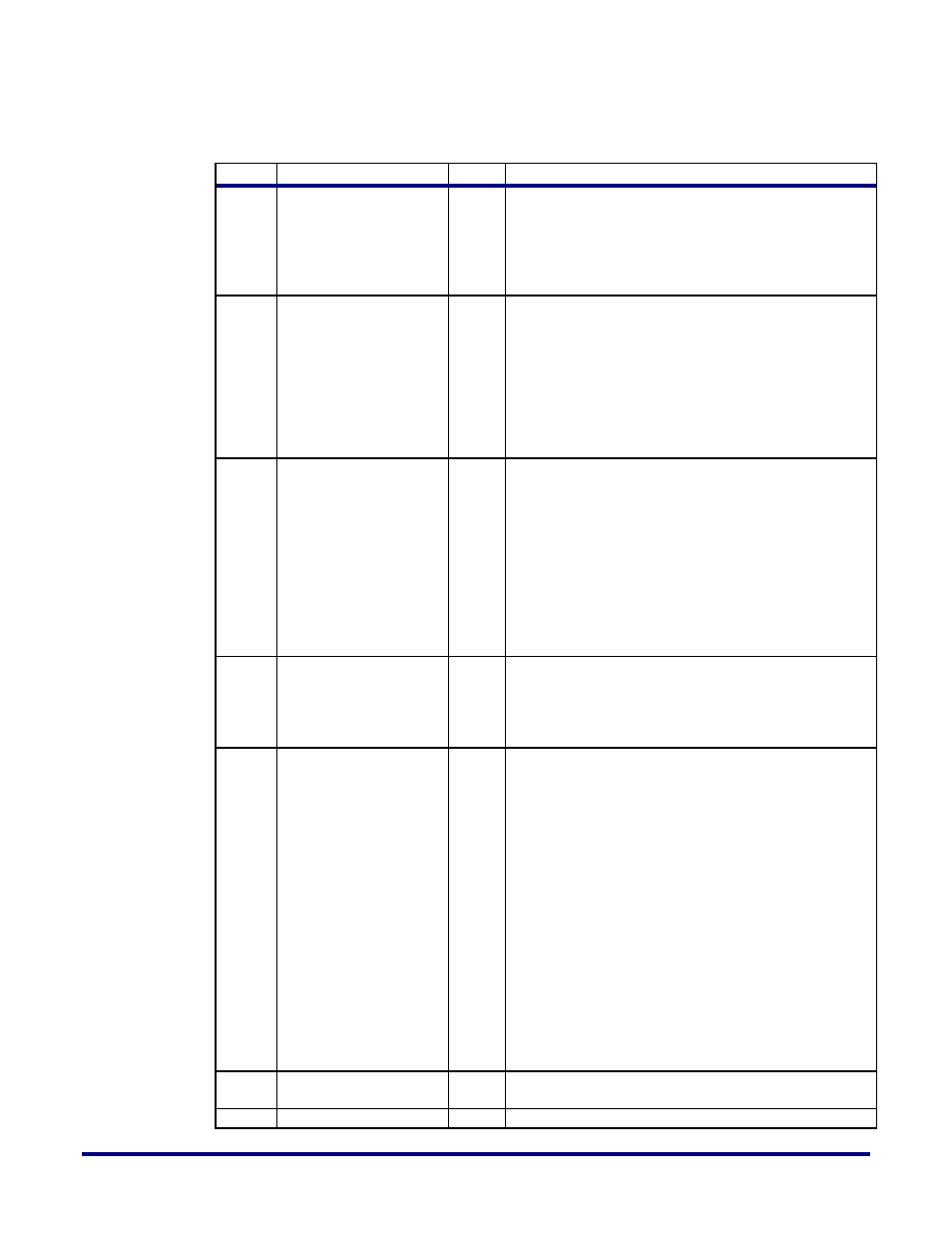

Table 42 – Achronix Speedster22i 10G/40G/100G Ethernet User Manual

Page 76

76

UG029, September 6, 2013

Table 42

– (SGMII PCS) IF_MODE Register Description

Bit(s)

Name

Type

Description

0

SGMII_ENA

RW

SGMII Mode Enable. When set to '0' (Reset Value),

the PCS operates in standard 1000Base-X Gigabit

mode, when set to '1', the PCS operates in SGMII

Mode.

If the bit is '0' the bits 1..4 of this register are

ignored.

1

USE_SGMII_AN

RW

Use the SGMII Auto-Negotiation Results to

Program the PCS Speed. When set to '0' (Reset

Value), the PCS operation should be programmed

with the register bit SGMII_SPEED and

SGMII_DUPLEX.

When '1', the PCS operation is automatically set

according to the Partner abilities advertised during

Auto-Negotiation.

Ignored when SGMII_ENA is set to '0'.

2 to 3

SGMII_SPEED

RW

SGMII Speed. When the PCS operates in SGMII

mode (SGMII_ENA set to '1') and when the PCS is

programmed not to be automatically configured

(USE_SGMII_AN set to '0'), sets the PCS speed of

operation (Bit 4:0]:

00: 10Mbps

01: 100Mbps

10: Gigabit

11: Reserved

Bits ignored when SGMII_ENA=0 or

USE_SGMII_AN=0.

4

SGMII_HDUPLEX

RW

SGMII Halfduplex Mode: When set (1), halfduplex

is enabled, when cleared, fullduplex is enabled

(default).

Note: halfduplex is not supported in this

implementation. This bit setting has no effect.

5

SGMII_PCS_ENABLE

RW

Enable SGMII/1000Base-X PCS instead of

XGMII/10GBase-R for the 10G MAC.

When set (1) the SGMII PCS layer becomes active

and the channel is configured for 1G mode of

operation. The other bits in this register have no

meaning if this bit is not set.

When cleared (0, default) the MAC operates in 10G

mode with an XGMII (internally) and 10GBase-R

PCS Layer.

Note: This bit only configures the datapath within

the combined MAC and PCS layers. It does not

change the PMA/SERDES module, externally to

the core. This must be controlled elsewhere to

adapt the correct interface width (10-bit) and speed

(125MHz).

Note: After setting this bit=1, a PCS soft reset

should be performed by writing bit15 of the PCS

control register.

5 to

15

Reserved

RO

-