Auto-negotiation control and status, Serial bus interface – Achronix Speedster22i 10G/40G/100G Ethernet User Manual

Page 18

18

UG029, September 6, 2013

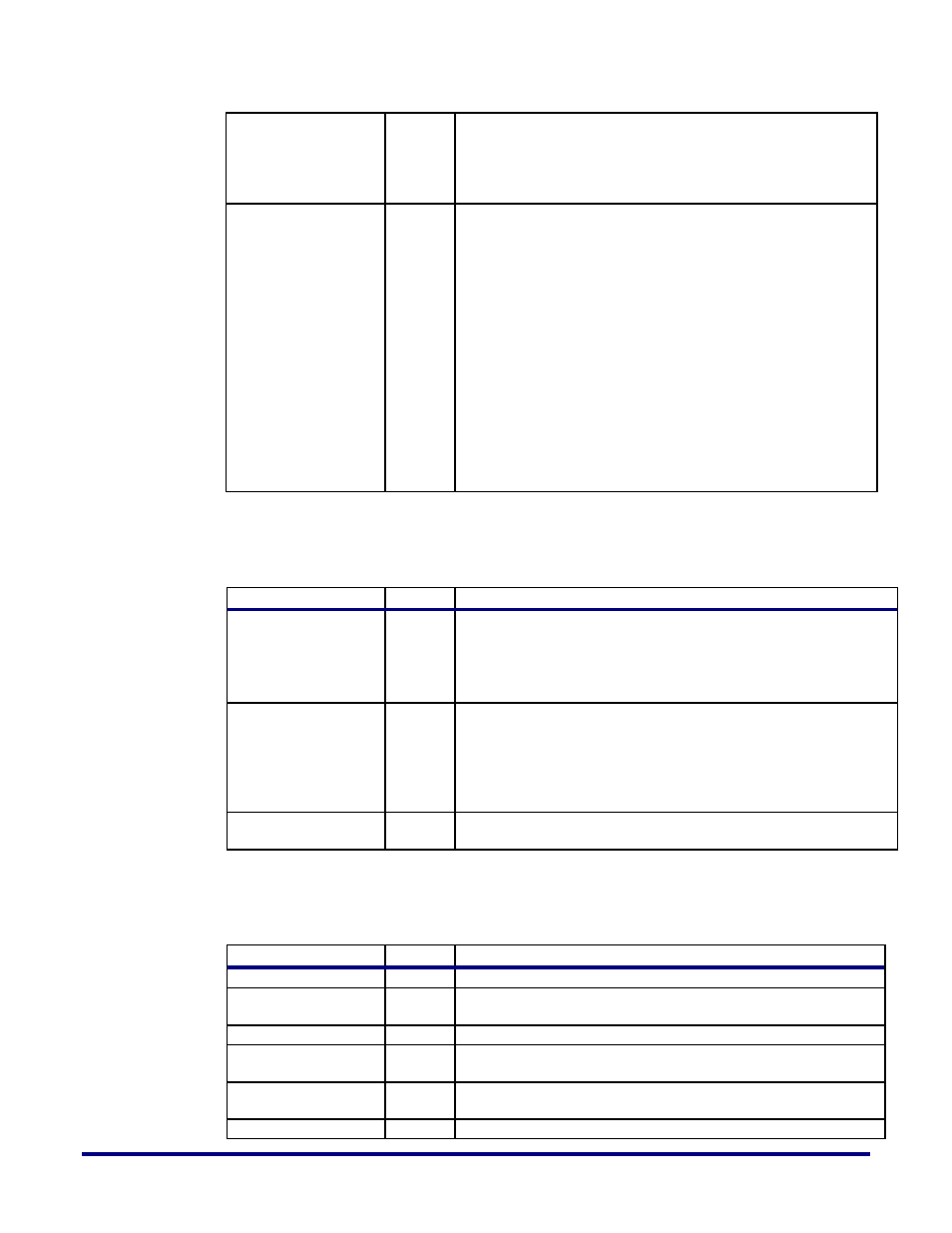

ff_tx_pfc_ack[11:0]

Out

Per segment Transmit Flow Control Acknowledge. Each

segment provides an ACK back to the application when it

samples the ff_tx_pfc_xoff inputs to indicate that a

PFC/Pause control frame is about to be sent according to

the provided status.

ff_rx_pfc_xoff

[11:0][ 7:0]

Out

12

– 8bit bus interfaces on a per segment Receive Flow

Control Status. For each of the 12 segments, an 8-bit

vector indicating the current pause status for the 8

priorities based on the internal pause quanta counters that

were set when a PFC control frame was received. When

asserted, it indicates that a PFC pause condition is in

place for that priority and the upstream core logic should

not schedule further traffic for this class. When zero, this

indicates the pause condition is no longer present and

traffic can be scheduled for this class.

In Link Pause Frame mode, Bit 0 is asserted (set to 1) to

indicate that the transmit path is paused as a result of a

received XOFF Pause frame. The signal deasserts, when

the pause timer has expired and the transmitter is allowed

to transmit frames again.

Auto-Negotiation Control and Status

Table 6

– Auto-Negotiation Control and Status (all synchronous to sbus_clk)

Signal Name

Mode

Description

an_ena[11:0]

In

Per segment Default Auto-

Negotiation Enable. If ‘1’, the auto-

negotiation process will start after reset de-assertion for the

respective segment. The application can also start the auto-

negotiation process by writing the

KXAN_CONTROL.an_enable

bit with ‘1’.

an_int[11:0]

Out

Per segment Auto-Negotiation Page Received Interrupt.

Asserted when a new page is received. Active only when the

Page Received Interrupt pin is enabled by writing the

KXAN_CONTROL.page_rcv_int_en bit with ‘1’.

See

Control Register Bits (KXAN_CONTROL) page 89 for details.

an_done[11:0]

Out

Per segment Auto-

Negotiation Done. If ‘1’, the auto-

negotiation process has completed.

Serial Bus Interface

Table 7

– Serial bus Interface (all synchronous to sbus_clk)

Signal Name

Mode

Description

sbus_clk

In

Register Access Clock.

reset_sbus_clk_n

In

Active low reset signal for the Ethernet MAC register

interface controlled by the sbus_clk clock domain.

i_sbus_data[1:0]

In

Carries read/write indication, address and data to write

i_sbus_req

In

Asserted for 9-cycles in case of read and for 11-cycles in

case of write

i_sbus_sw_rst

In

Active high reset signal for the Serial Bus Interface

controlled by the sbus_clk clock domain.

o_sbus_ack

Out

Acknowledgment from register i/f once read or write is