Tx/rx lane receive equalization registers – Achronix Speedster22i 10G/40G/100G Ethernet User Manual

Page 94

94

UG029, September 6, 2013

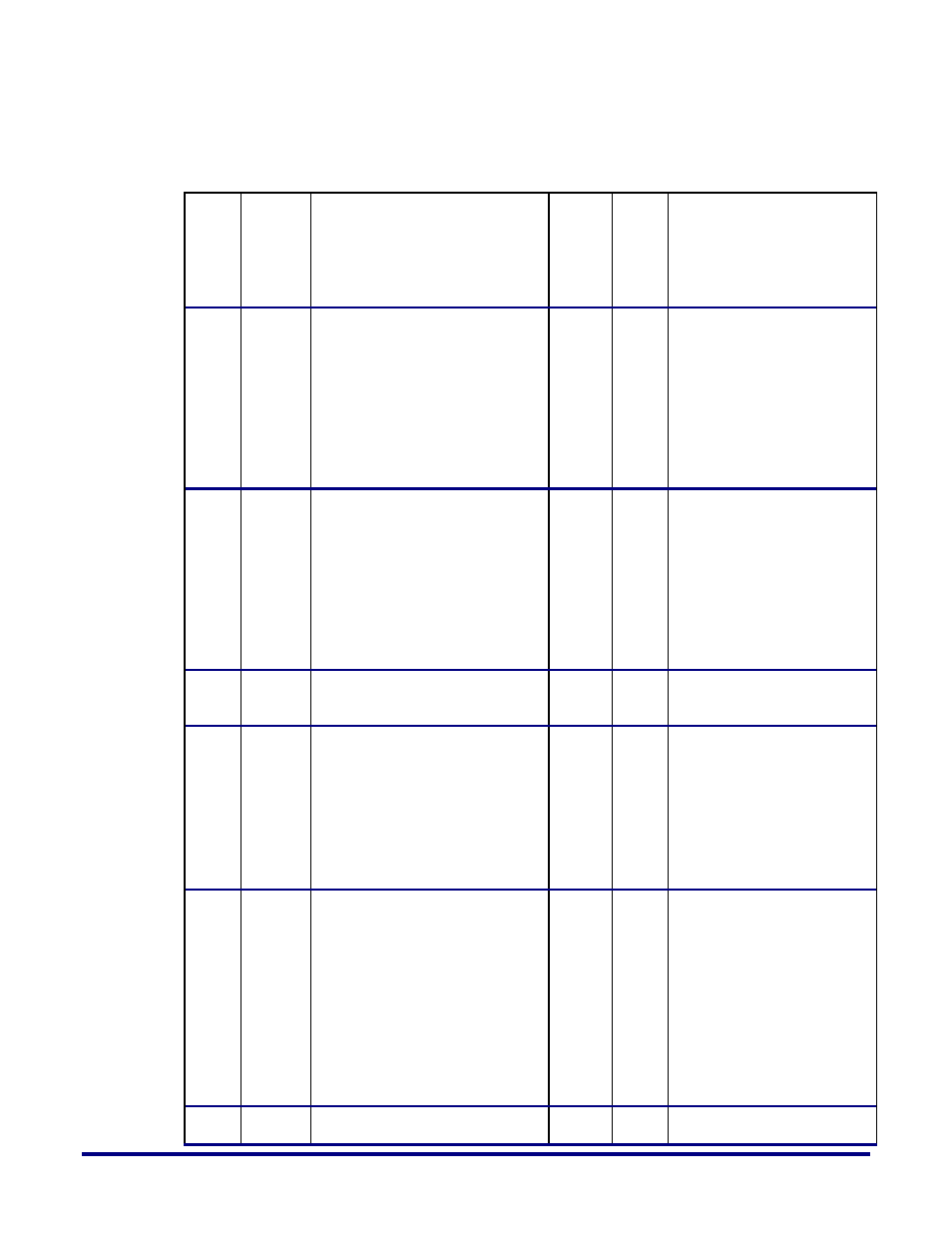

TX/RX Lane Receive Equalization Registers

Table 58

– TX/RX Lane Receive Equalizer Control Registers

Reg

Pg.

(hex)

Reg

Offset

[Start

Bit:

End

Bit]

(hex)

Register Field Name

Reg

Type

RW/R

Defau

lt

Value

(hex)

Description

0

18[2:0]

RXCALEQ_DCGAIN

RW

0

RX agc high frequency dc

gain:

-3'b000: -3dB

-3'b001: -2.5dB

-3'b010: -2dB

-3'b011: -1.5dB

-3'b100: -1dB

-3'b101: -0.5dB

-3'b110: -0dB

-3'b111: 0.5dB

0

18[5:3]

RXCALEQ_DFEPSTAPF3DB

RW

7

DFE post-shaping tap 3dB

frequency

-3'b000: 684MHz

-3'b001: 576MHz

-3'b010: 514MHz

-3'b011: 435MHz

-3'b100: 354MHz

-3'b101: 281MHz

-3'b110: 199MHz

-3'b111: 125MHz

0

56[3:3]

RXCALEQ_LOCWREN

RW

1

RX equalizer control

signals override enable.

Active Low

0

19[2:0]

RXCALEQ_DFEPSTAPGAIN

RW

0

DFE post-shaping tap gain

0: no pulse shaping tap

1: -24mVpeak

2: -45mVpeak

3: -64mVpeak

4: -80mVpeak

5: -93mVpeak

6: -101mVpeak

7: -105mVpeak

0

19[6:3]

RXCALEQ_DFETAP1GAIN

RW

0

DFE first tap gain control

-4'b0000: +1mVpeak

-4'b0001: +10mVpeak

...

-4'b0110: +55mVpeak

-4'b0111: +64mVpeak

-4'b1000: -1mVpeak

-4'b1001: -10mVpeak

..

-4'b1110: -55mVpeak

-4'b1111: -64mVpeak

0

1A[3:0]

RXCALEQ_DFETAP2GAIN

RW

8

DFE second tap gain

control