Credit handling, Receive direction: fifo to application, Figure 10: credit based application interface – Achronix Speedster22i 10G/40G/100G Ethernet User Manual

Page 32

32

UG029, September 6, 2013

Credit Handling

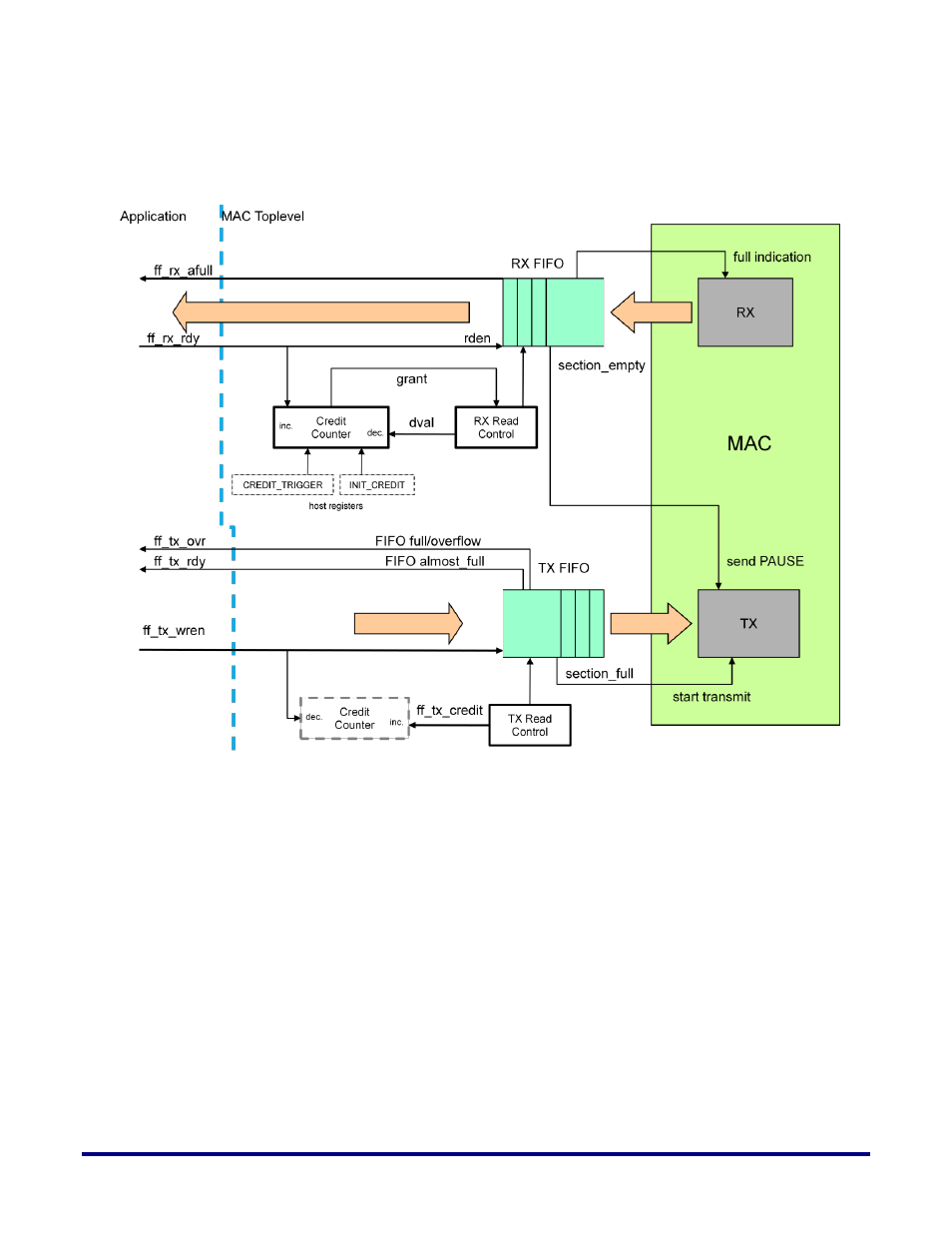

The following figure provides an overview of the credit based application interface.

Figure 10: Credit based application interface

Receive Direction: FIFO to Application

Internally, the receive datapath FIFO implements a credit counter which defines how many

words the FIFO is allowed to deliver to the application. The credit counter is initialized by

the application at startup, to the maximum burst acceptable by the application (see registers

INIT_CREDIT and CREDIT_TRIGGER).

Once the credit counter has been initialized, the FIFO will provide data to the application as

long as it has credits available and the ff_rx_rdy signal is asserted. The user asserts ff_rx_rdy

to signal to the receive interface that it has consumed the data presently at the ff_rx_data

output. The user should monitor the ff_rx_afull flag if it is not able to continuously read the

received data. Alternatively, if the application can guarantee it is always operating faster

than the MAC will receive data, it may choose to permanently keep the ff_rx_rdy signal high.