Fifo thresholds, Fifo sections behavior (watermarks) – Achronix Speedster22i 10G/40G/100G Ethernet User Manual

Page 43

UG029, September 6, 2013

43

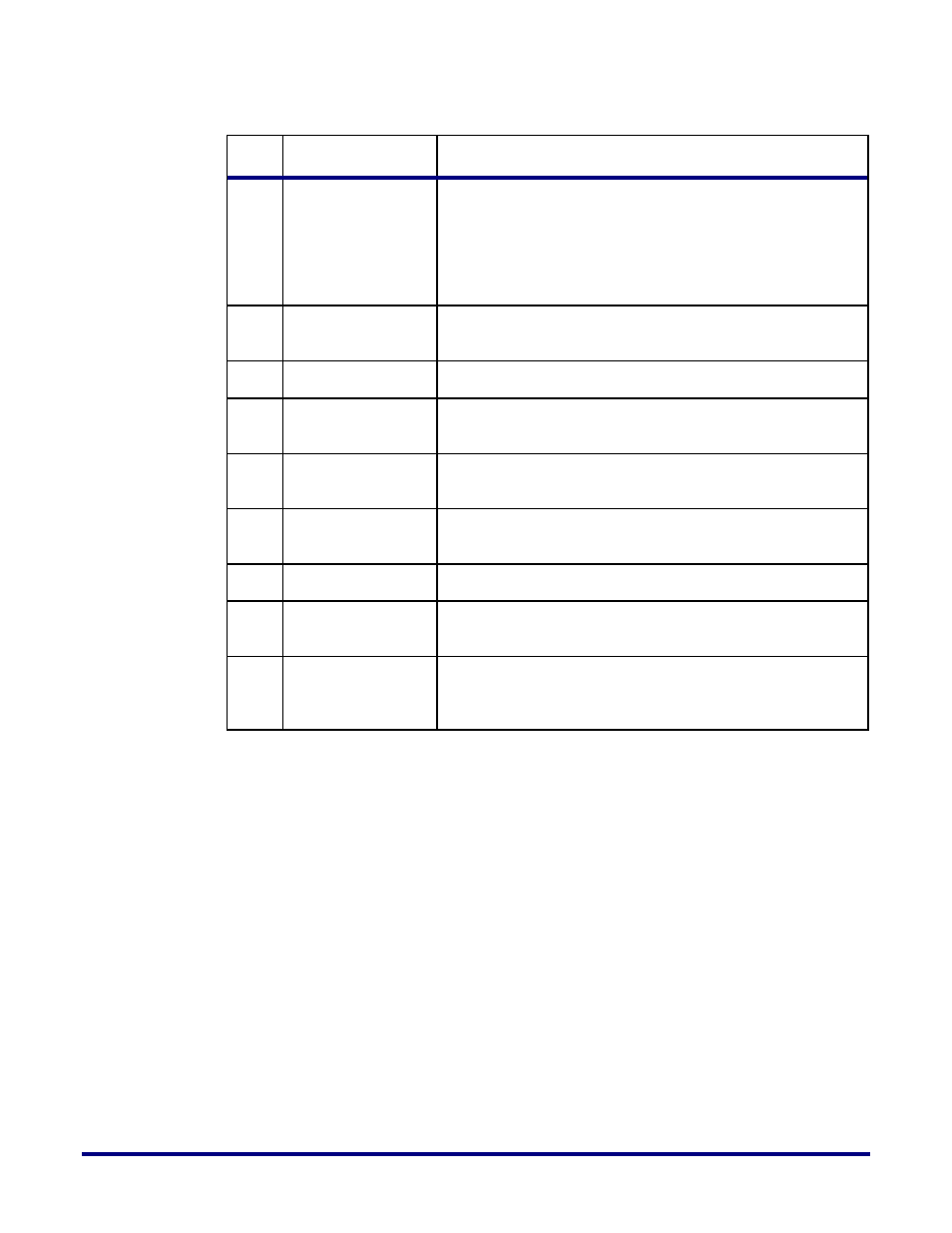

Table 22

– Frame Status Word Bits

Bit #

Name

Description

0

LENGTH_ERROR

Set to ‘1’ if the frame has an invalid length. This can be

either a too long frame (length greater than the value

programmed in register FRM_LENGTH), or a frame which

has a different amount of payload than specified in the

frame's payload length field.

Frames below 64 octets in length are never delivered to the

FIFO interface.

1

CRC_ERROR

Set to ‘1’ if the frame was received with a CRC field that did

not match the CRC calculated by the MAC Core. The frame

is invalid.

2

PHY_ERROR

Set to ‘1’ if the frame was received with an unknown control

character. The frame is invalid.

3

FIFO_OVERFLOW

Set to ‘1’ if a FIFO overflow was detected during frame

reception. The received frame is truncated by the MAC

Core and is invalid.

4

FAULT_SEQ

Set to ‘1’ if a Sequence Error (local or remote fault) has

been received from the PHY during frame reception. The

frame is invalid.

5

STACKED_VLAN

Set to ‘1’ to indicate that the frame is a Stacked VLAN

frame. This information can be used to switch the received

frame to dedicated VLAN frames processing engines.

6

TRANSMIT_ERR

Set to ‘1’ if a transmit error control character (0xFE) has

been received from the line. The frame is invalid.

7

VLAN

Set to ‘1’ to indicate that the frame is a VLAN frame. This

information can be used to switch the received frame to

dedicated VLAN frames processing engines.

23:8

PAYLOAD_LEN

Frame payload length in bytes or type information. The

copied value of the frame's length/type field. For VLAN

frames the value immediately following the 4-octet VLAN

tag is copied.

FIFO Thresholds

The Core implements programmable FIFO thresholds that provide the possibility to

dynamically change the FIFO operation and fixed Almost Full and Almost Empty thresholds

for FIFO overflow / underflow protection.

FIFO Sections Behavior (Watermarks)

The FIFO logic offers to set high- and low-watermarks by setting the configuration registers

RX_FIFO_SECTIONS and TX_FIFO_SECTIONS. The sections are defined in steps of segment

data words (10G: 32-bit, 40G: 128-bit, 100G: 384-bit).

tx/rx_section (section available) defines a low-watermark that is used to assert an

internal signal when this amount of data is available in the FIFO.

tx/rx_section_e (section empty) defines a high-watermark that is used to de-assert an

internal signal when the FIFO is filled to this level and above.