Interface signal descriptions, Global signals, Receive fifo interface – Achronix Speedster22i 10G/40G/100G Ethernet User Manual

Page 13

UG029, September 6, 2013

13

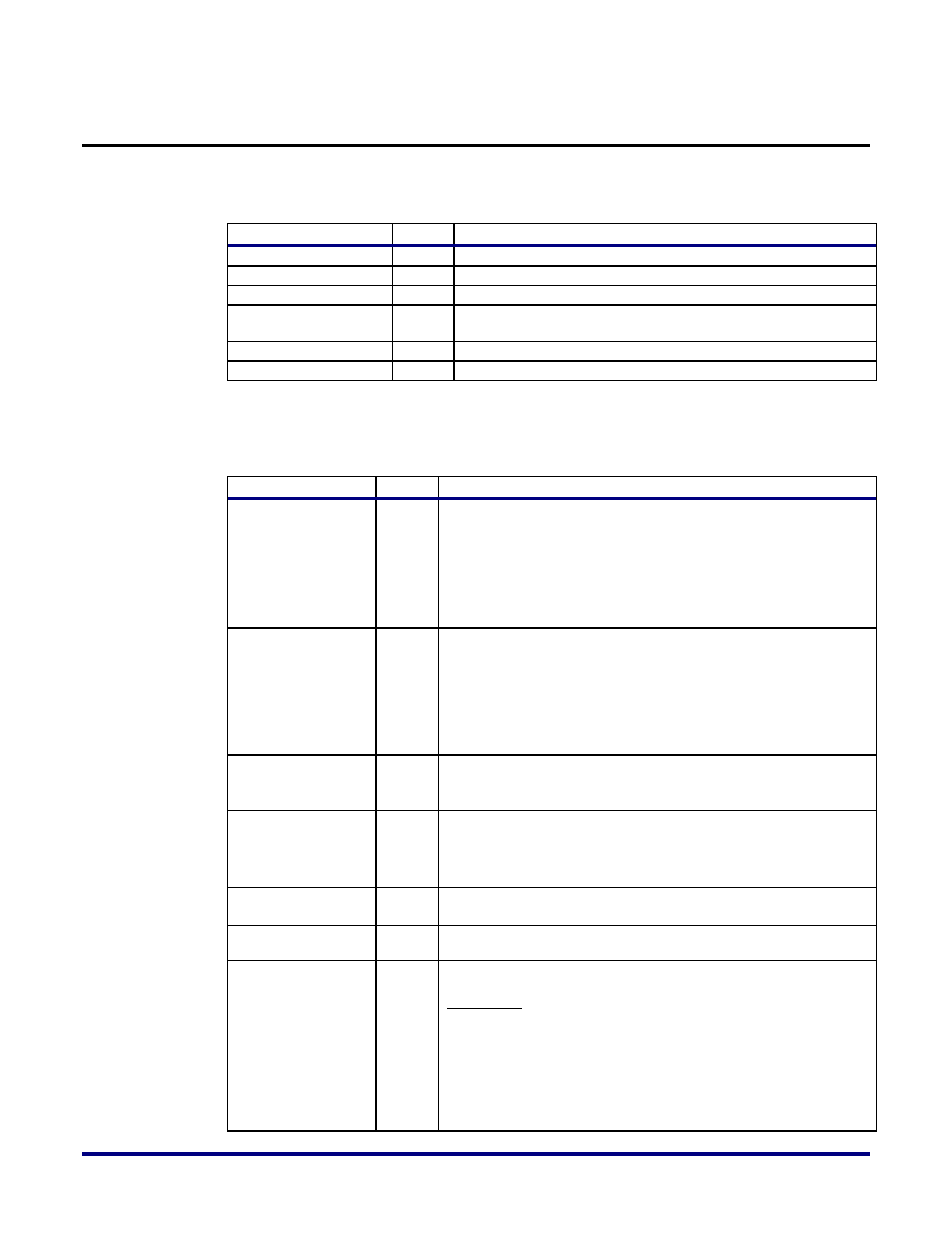

Interface Signal Descriptions

Global Signals

Table 1

– Global Signals

Signal Name

Mode

Description

ref_clk

In

Reference Clock. Must be at least 652 MHz +/- 100ppm.

reset_n

In

Active low hard reset for all SerDes channels.

reset_ref_clk_n

In

Active low reset signal for ref_clk clock domain.

reset_ts_clk_n

In

Active low reset signal for ts_clk clock domain (if ts_clk is

used, see below).

reset_ff_tx_clk_n[2:0]

In

Active low reset signal for ff_tx_clk[2:0] clock domains.

reset_ff_rx_clk_n[2:0]

In

Active low reset signal for ff_rx_clk[2:0] clock domains.

Receive FIFO Interface

Table 2

– Receive FIFO Interface (All syncrounous to sys_clk at user interface)

Signal Name

Mode

Description

sys_clk

In

FPGA fabric System Clock. All the FIFO signals are

synchronized on sys_clk rising edge. The minimum

frequency for the system clock is a function of the interface

rate:

10G: at least 155 MHz

40G: at least 177 MHz

100G: at least 295 MHz

ff_clk[2:0]

In

FIFO Reference Clocks per FIFO group. Can be set to any

value required to get the required bandwidth on the FIFO

768-Bit interface. Can be independent from the System

clock, however the FIFO clock has to be at least 357.15 MHz

to allow for the start of frame to be always aligned on lane 0

for 40G mode and may be relaxed to at least 320.51 MHz for

the 10G or 100G modes.

ff_rx_data

[767:0]

Out

Receive Data.

Refer to the ‘Fabic FIFO Interface’ for the

details of how to map this 768-bit bus to the individual

10/40/100G channels.

ff_rx_dval[11:0]

Out

Receive Data Valid per segment. Asserted (set to 1) by the

MAC to indicate that data on ff_rx_data, ff_rx_sop,

ff_rx_eop, ff_rx_mod, ff_rx_err, ff_rx_vlan,

ff_rx_err_stat and ff_rx_ts is valid.

ff_rx_sop[11:0]

Out

Receive Start of Frame per segment. Set to 1 when the first

data word of a frame is driven on ff_rx_data.

ff_rx_eop[11:0]

Out

Receive End of Frame per segment. Set to 1 when the final data

word of a frame is driven on ff_rx_data.

ff_rx_mod

[(12*6)-1:0]

Out

Receive Word Modulo per segment. Indicates which portion of the

final frame word is valid:

Bit 543210

000000 : ff_rx_data[63:0]/[255:0]/[511:0] is valid (for

10/40/100G)

000001 : ff_rx_data[7:0] is valid

000010 : ff_rx_data[15:0] is valid

000011 : ff_rx_data[23:0] is valid

000100 : ff_rx_data[31:0] is valid

000101: ff_rx_data[39:0] is valid