Rockwell Automation 1794-APBDPV1 FLEX I/O PROFIBUS Adapter User Manual User Manual

Page 74

Publication 1794-UM064B-EN-P - May 2014

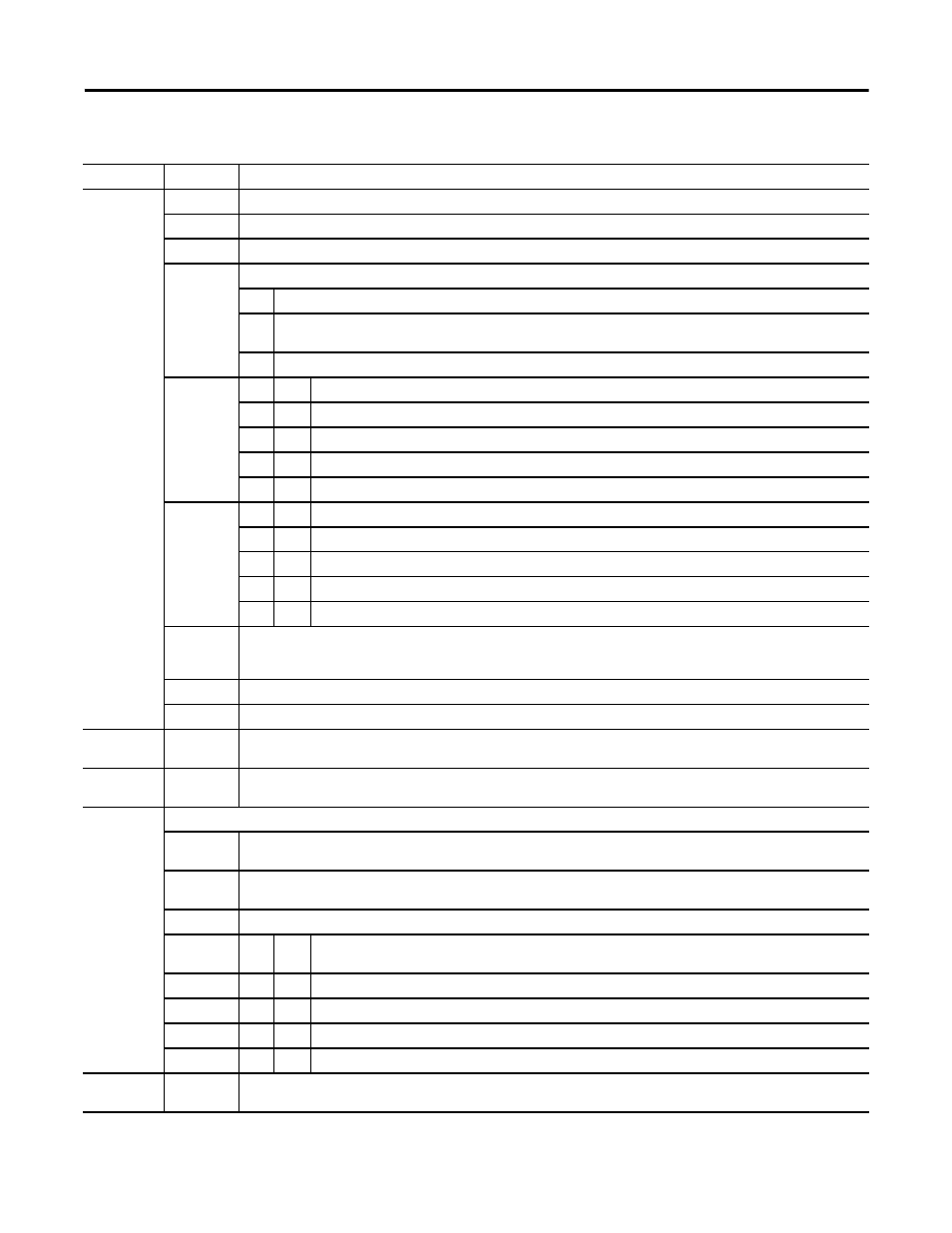

62 Communicate With Your Module

Write Word 2 Bit 03

Counter Preset bit – A positive edge on this bit moves the value in Preset X to Counter X, independent of Preset Enable.

Bit 04

Preset Enable bit – When set (1), a positive edge on Z preloads Counter X = Preset X, independent of Cal Enable.

Bit 05

Count Enable bit – When set (1), the incremental encoder is counting.

Bits 06…08

(06…10)

Calibration Control bits – bits 06, 07 and 08.

06

Enable bit – When set (1), the counter can be calibrated.

07

Direction bit – When set (1), calibration is performed in a negative direction; when reset (0), calibration is

performed in a positive direction.

08

Reset bit – Calibration is acknowledged and a new calibration is enabled on a positive edge on this bit.

Bits 09…10

(11…12)

10

09

Gate Control bits

0

0

No gate function on input G.

0

1

Counting only if G is high (active).

1

0

Counting only if G is low (inactive).

1

1

Calibration if G is high (active).

Bits 11…12

(13…14)

12

11

Latch Control bits

0

0

Save the counter value on the positive edge of Z (if Stored X = 0).

0

1

Save the counter value on the positive edge of G (if Stored X = 0).

1

0

Save the counter value on the negative edge of G (if Stored X = 0).

1

1

Save the counter value on the positive and negative edges of G (if Stored X = 0).

Bit 13 (15)

Rollover bit – When set (1), the counter counts up to the preset and then restarts at 0. If this bit is reset (0) (not rollover),

the rollover preset value = FFFF

hex = 65535 (decimal).

Bit 14 (16)

Ch 1 Preset Reset bit – A positive edge on this bit resets Stored X in Signals.

Bit 15 (17)

Ch 1 Store Reset bit - A positive ege on this bit resets Preset Reached in Signals.

Write Word 3 Bits 00…15

(00…17)

Ch 0 Preset – Value to load or compare with counter 0.

Write Word 4 Bits 00…15

(00…17)

Ch 1 Preset – Value to load or compare with counter 1.

Write Word 5 Filter Selection

Bit 00

Ch 0 Filter Enable – When set (1), and a counter 0 is in mode 000 (pulse counting), signal A0 is filtered by a digital low

pass filter with selectable filter constant.

Bit 01

Ch 1 Filter Enable – When set (1), and a counter 1 is in mode 000 (pulse counting), signal A1 is filtered by a digial low

pass filter with selectable filter constant.

Bit 02…07

Unused.

Bits 08…09

(10…11)

09

(11)

08

(10)

Filter bits – This constand is common to both counters.

0

0

73.5 kHz or minimum 0.007 ms pulsewidth.

0

1

37.8 kHz or minimum 0.013 ms pulsewidth.

1

0

12.8 kHz or minimum 0.04 ms pulsewidth.

1

1

1.2 kHz or minimum 0.4 ms pulsewidth.

Write Words

6…7

Bits 00…15

(00…17)

Not used – set to 0.

1794-ID2 Pulse Counter Module Word/Bit Definitions for Block Transfer Read Words

Word

Bit

Definition