Rockwell Automation 1794-APBDPV1 FLEX I/O PROFIBUS Adapter User Manual User Manual

Page 64

Publication 1794-UM064B-EN-P - May 2014

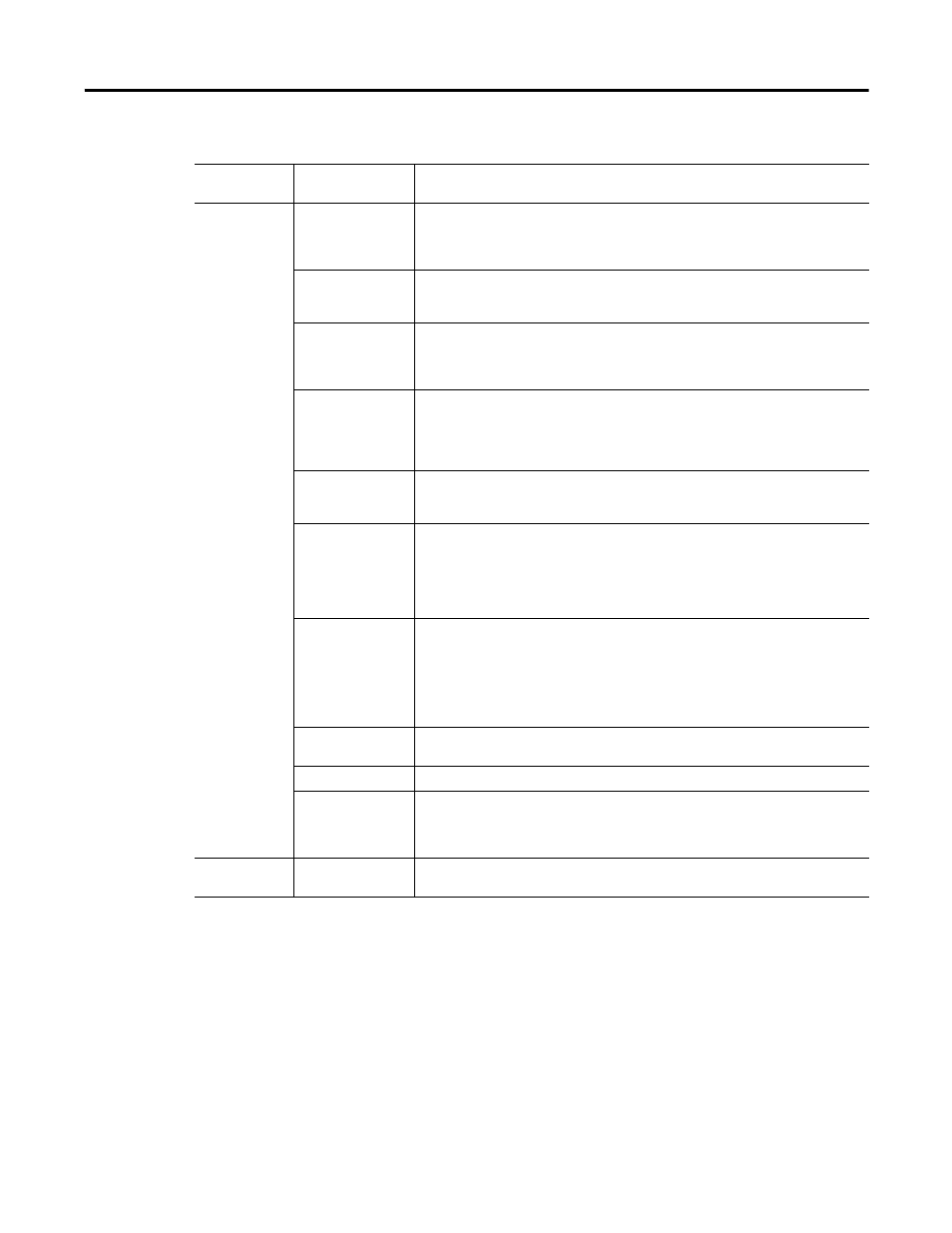

52 Communicate With Your Module

Write Word 6

Bits 00…03

Calibrate bit – When this bit is set (1), the channel can be calibrated using the

calibration clock bit (CK). Bit 00 corresponds to output channel 0, bit 01 corresponds to

output channel 1, bit 02 corresponds to output channel 3, bit 03 corresponds to output

channel 4.

Bit 04

Gain/Offset Calibration bit (GO) – When this bit is cleared, a 0 to 1 to 0 transition of

the CK bit performs on offset calibration. When this bit is set (1), the module is directed

to do a gain calibration.

Bit 05

Calibration Clock bit (CK) – When this bit is set to 1 (calibration mode), the

calibration coefficient for the selected channels is accepted. When this bit is reset (0),

the accepted calibration coefficients for the selected channels are stored, applied, and

the calibration mode exited. Monitor status bits DN and BD for successful calibration.

Bit 06

Quick Calibration bit (QK) – Normally reset (0). When this bit is set (1) during a

calibration sequence, the calibration coefficient is stored to all related configurations

for the selected channels.

NOTE: Although this method of calibration quickly calibrates the selected channels,

they will not be within the rated accuracy of the module.

Bit 07

Revert to Defaults bit (RV) – Normally reset (0). When set (1) during a calibration

procedure, default values for selected channels are used for the calibration coefficient.

NOTE: They will not be within the rated accuracy of the module.

Bits 08…11

(10…13)

Request for Hold Outputs (Q) – Channel request bits that instruct and output to hold

its output level when EN transitions from 1 to 0 to 1. When EN is 0, outputs go to a save

state dictated by S1/S0. When EN returns to 1, the outputs will hold their level until the

output data equals the output level. P0...P3 indicates channels holding. Output read

back data shows what level is being held. Q0 = bit 08 (10) = channel 0; Q1 = bit 08 (10) =

channel 1, and so on.

Bit 12 (14)

Interleave Interrupt (IT) – This bit, when set (1), permits interleaving of module

interrupts ensuring exchange of critical data when channels are configured for their

fastest update times. RTSI and "no low pass filter" must be 0 in order for the module to

recognize this feature. This groups data update rates for all channels to the slowest

configuration setting of any of the channels. In addition, channel update rates for all

channels with a 7.5 ms update rate are reduced to 5.0 ms. When reset (0), real time

sampling and filter features are enabled.

Bit 13 (15)

Transparent bit (TR) – This bit, when set (1), permits configuration to be changed

without using the IC bit.

Biut 14 (16)

Set to 1.

Bit 15 (17)

Initiate Configuration bit (IC) – When set (1), instructs this the module to enter

configuration mode. Present configuration data prior to or coincident with IC being set.

Once IC returns to 0, the configuration is applied and any subsequent configuration

information is ignored until IC is toggled.

Write Words

7 and 8

Bits 00…15

(00…17)

Not used.

1794-IF4I Isolated Analog Input Module Word/Bit Descriptions

Write Word

Decimal Bit

(Octal Bit)

Definition