Rockwell Automation 1771-QA Stepper Positioning Assembly User Manual User Manual

Page 59

3–37

Programming and Operation

Publication 1771-UM002A–EN–P – May 2000

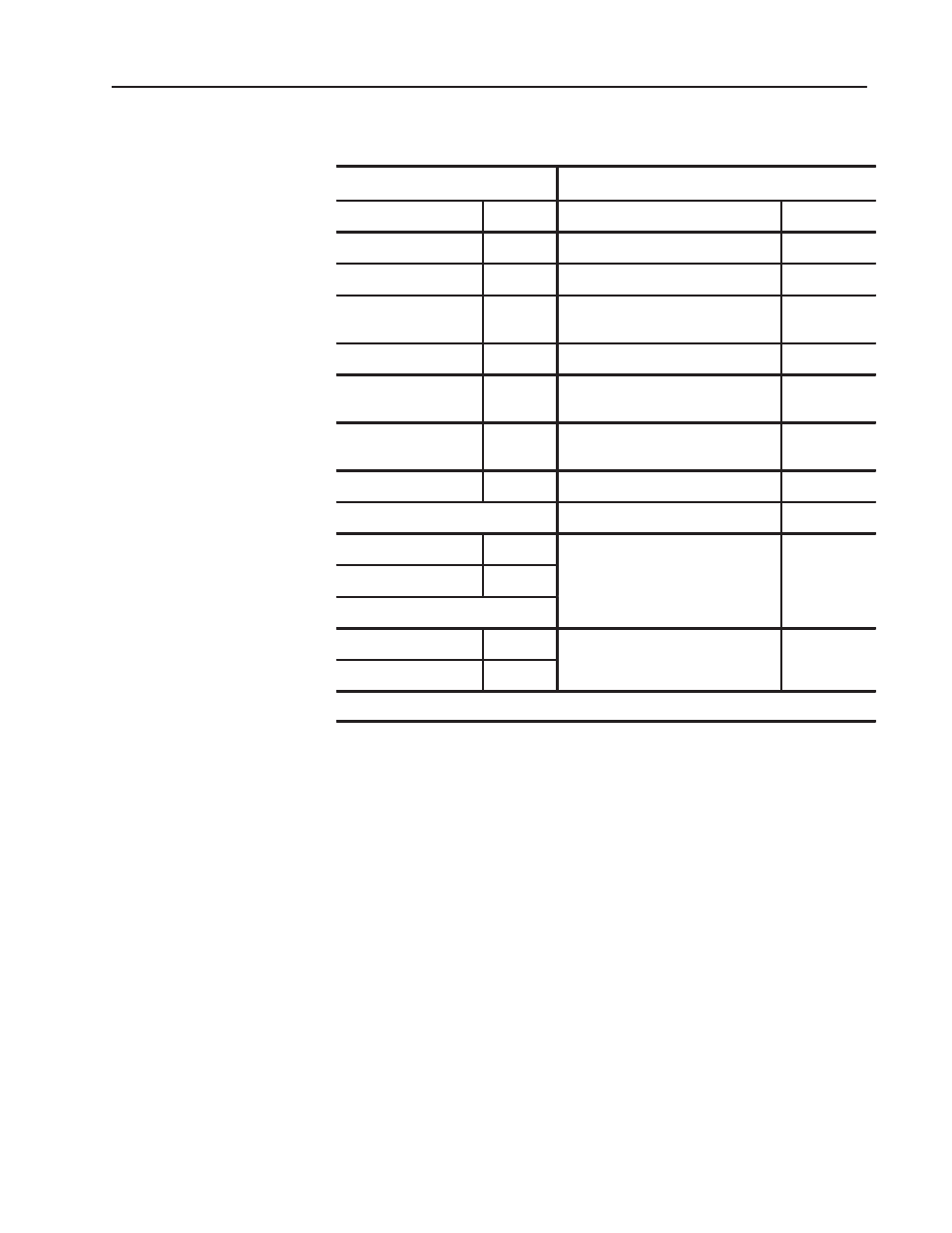

Table 3.B

Corresponding Handshake Bits

Moveset Control Word

Moveset Control Word

Command

Bit

Function

Bit

Start

00

Command verify

00

Reset

04

1

Reset

05

Stop

06

1

Programmed Stop and Command

Verify

06

00

Offset

13

Command Verify

00

Software jog reverse

14

Jog reverse and Command verify

14

00

Software jog forward

15

Jog forward and Command verify

15

00

Override

17

Command verify

00

MS Preset Word

Command

Bit

Initialization preset

17

Command verify

00

Single Move Control Word

Command

Bit

Load jog

03

Command verify

00

1

Once set, the reset and stop status bits remain set until another move begins.

Block Transfer Timing

The time required for a block transfer read or write operation for

PLC-2 Family processors depends on the system scan time(s), the

number of words to be transferred, the I/O configuration and the

number of enabled block transfer instructions in the ladder diagram

program during any program scan. A block transfer module will not

accept another transfer until finished processing the previous

transfer. For a worst case calculation of the time between block

transfers, assume that the number of enabled block transfer

instructions during any program scan is equal to the number of block

transfer modules in the system. Also assume that the stepper

controller module is operating in default mode so that 64 words or 10

words are transferred in the write or read operation, respectively.

The stepper controller module will toggle, when done, from one

operation to the other in the next program scan.