Festo Кабели и принадлежности User Manual

Page 62

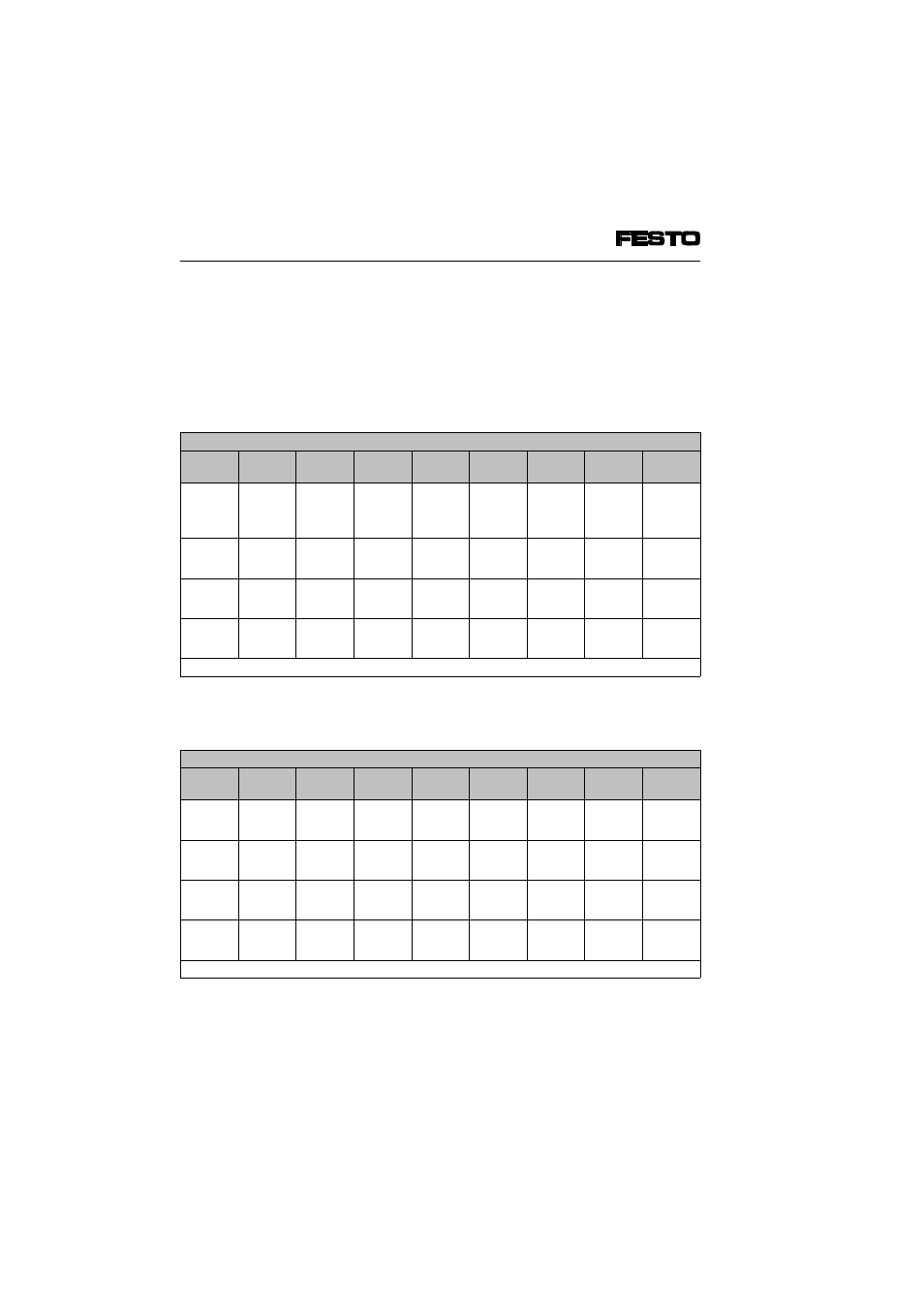

4.4.2 Summary of the I/O addresses of the SPC200-COM-IBS

Internal I/O addresses in start/stop mode

The configured outputs of the master are mapped on

the input bits.

Input bits (I10.0 ... I13.15)

1)

Byte

Bit 7

Bit 15

Bit 6

Bit 14

Bit 5

Bit 13

Bit 4

Bit 12

Bit 3

Bit 11

Bit 2

Bit 10

Bit 1

Bit 9

Bit 0

Bit 8

n

n+1

I10.7

I10.15

I10.6

I10.14

I10.5

I10.13

Sync_IB

I10.12

Sync_IA

I10.11

Stop

I10.10

Start/

Reset

I10.9

Enable

I10.8

n+2

n+3

I11.7

I11.15

I11.6

I11.14

I11.5

I11.13

I11.4

I11.12

I11.3

I11.11

I11.2

I11.10

I11.1

I11.9

I11.0

I11.8

n+4

n+5

I12.7

I12.15

I12.6

I12.14

I12.5

I12.13

I12.4

I12.12

I12.3

I12.11

I12.2

I12.10

I12.1

I12.9

I12.0

I12.8

n+6

n+7

I13.7

I13.15

I13.6

I13.14

I13.5

I13.13

I13.4

I13.12

I13.3

I13.11

I13.2

I13.10

I13.1

I13.9

I13.0

I13.8

1)

Address assignment as seen by the SPC200

The internal outputs of the field bus module are

mapped on the configured inputs of the master.

Output bits (Q10.0 ... Q13.15)

1)

Byte

Bit 7

Bit 15

Bit 6

Bit 14

Bit 5

Bit 13

Bit 4

Bit 12

Bit 3

Bit 11

Bit 2

Bit 10

Bit 1

Bit 9

Bit 0

Bit 8

n

n+1

Q10.7

Q10.15

Q10.6

Q10.14

Q10.5

Q10.13

MC_B

Q10.12

MC_A

Q10.11

Sync_OB

Q10.10

Sync_OA

Q10.9

Ready

Q10.8

n+2

n+3

Q11.7

Q11.15

Q11.6

Q11.14

Q11.5

Q11.13

Q11.4

Q11.12

Q11.3

Q11.11

Q11.2

Q11.10

Q11.1

Q11.9

Q11.0

Q11.8

n+4

n+5

Q12.7

Q12.15

Q12.6

Q12.14

Q12.5

Q12.13

Q12.4

Q12.12

Q12.3

Q12.11

Q12.2

Q12.10

Q12.1

Q12.9

Q12.0

Q12.8

n+6

n+7

Q13.7

Q13.15

Q13.6

Q13.14

Q13.5

Q13.13

Q13.4

Q13.12

Q13.3

Q13.11

Q13.2

Q13.10

Q13.1

Q13.9

Q13.0

Q13.8

1)

Address assignment as seen by the SPC200

4. Commissioning

4-28

SPC200-COM-IBS 0503a