Rainbow Electronics DS2141A User Manual

Page 25

DS2141A

021997 25/35

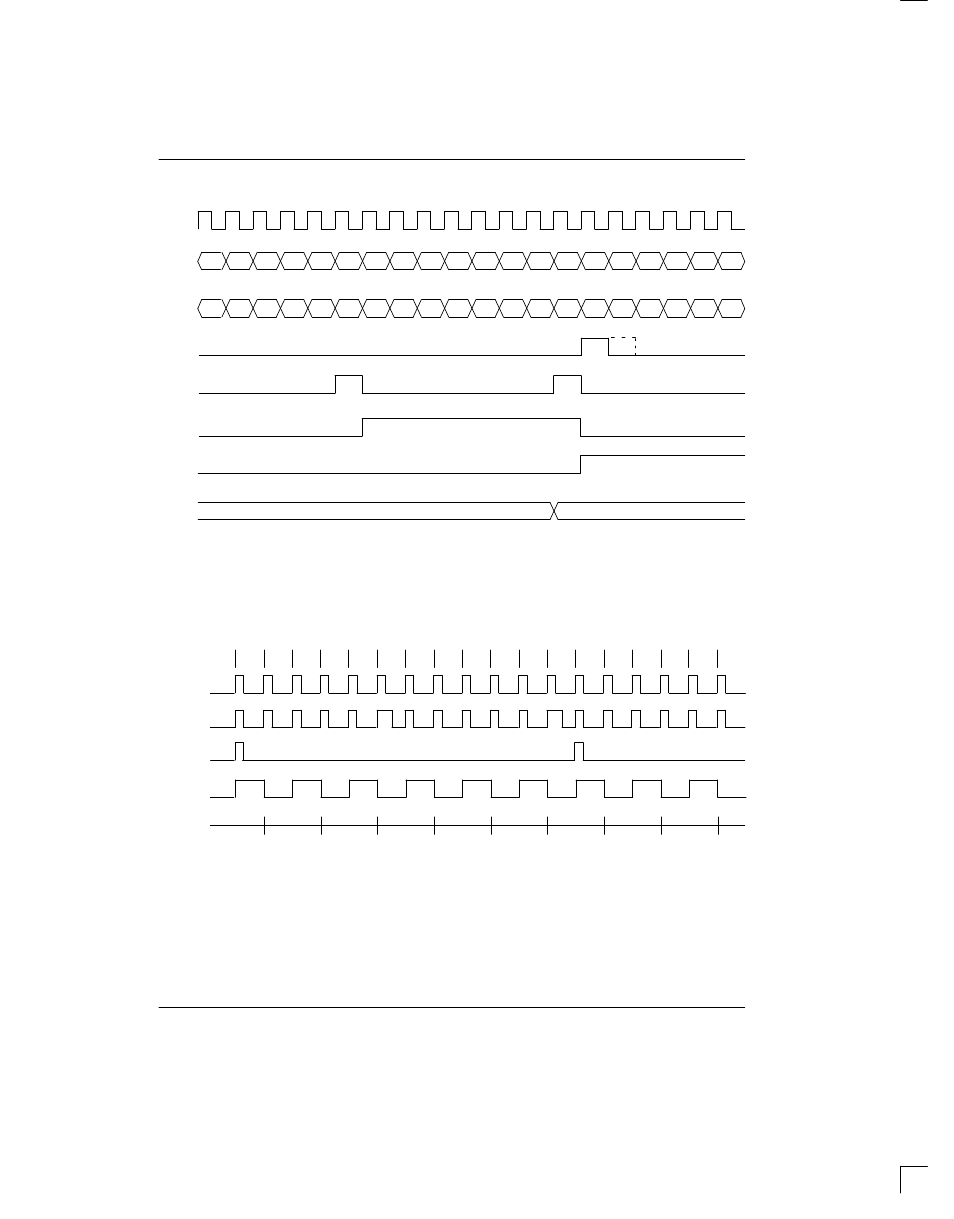

RECEIVE SIDE BOUNDARY TIMING (WITH ELASTIC STORE(S) DISABLED)

RCLK

RPOS

1

,

RNEG

TSER/

RSER

1

RSYNC

RCHCLK

RCHBLK

2

RLCLK

RLINK

LSB

F

MSB

LSB MSB

LSB MSB

CHANNEL 1

CHANNEL 2

LSB MSB

LSB

MSB

F

CHANNEL 23

CHANNEL 24

CHANNEL 1

NOTES:

1. There is a 13 RCLK delay from RPOS, RNEG to RSER.

2. RCHBLK is programmed to block Channel 24.

TRANSMIT SIDE D4 TIMING

1

2

3

4

5

6

7

8

9

10

11

12

1

2

3

4

5

FRAME#

TSYNC

1

TSYNC

2

TSYNC

3

TLCLK

TLINK

4

NOTES:

1. TSYNC in the frame mode (TCR2.3=0) and double–wide frame sync is not enabled (TCR2.4=0).

2. TSYNC in the frame mode (TCR2.3=0) and double–wide frame sync is enabled (TCR2.4=1).

3. TSYNC in the multiframe mode (TCR2.3=1).

4. TLINK data (S–bit) is sampled during the F–bit position of even frames for insertion into the outgoing T1 stream

when enabled via TCR1.2.

- MAX12005 (14 pages)

- MAX7058 (14 pages)

- MAX9995 (13 pages)

- MAX7034 (13 pages)

- MAX7033 (16 pages)

- MAX9476 (8 pages)

- MAX9486 (8 pages)

- MAX14821 (29 pages)

- MAX9489 (11 pages)

- MAX9491 (11 pages)

- DS2130Q (22 pages)

- DS21458 (270 pages)

- DS3131 (174 pages)

- DS26502 (125 pages)

- DS2153Q (48 pages)

- DS26503 (123 pages)

- DS2186 (11 pages)

- DS1842A (6 pages)

- DS3134 (203 pages)

- DS1876 (69 pages)

- DS1874 (88 pages)

- DS31256 (181 pages)

- DS3184 (13 pages)

- DS2154 (69 pages)

- DS26504 (128 pages)

- DS3164 (12 pages)

- DS1852 (25 pages)

- DS2181A (32 pages)

- DS2151Q (46 pages)

- DS1843 (8 pages)

- DS2165Q (17 pages)

- DS3170 (233 pages)

- DS2180A (36 pages)

- DS2172 (20 pages)

- DS2152 (79 pages)

- DS1841 (16 pages)

- DS2182A (22 pages)

- DS2143Q (40 pages)

- DS2132A_Q (17 pages)

- DS1862 (42 pages)

- DS26519 (310 pages)

- DS2188 (11 pages)

- DS1875 (92 pages)

- DS33M33 (20 pages)