At83c26 – Rainbow Electronics AT83C26 User Manual

Page 53

53

7511B–SCR–10/05

AT83C26

Reset value = 0x 0X00 1000

Notes:

1. When CKS5 value is changed a special logic insures no glitch occurs on the CCLK5 pin and

actual configuration changes can be delayed by half a period to two periods of CCLK5.

2. CCLK5 must be stopped with CKSTOP5 bit before switching from CKS5 = (0, 1, 2, 3, 6, 7) to

CKS5 = (4, 5) or vice versa.

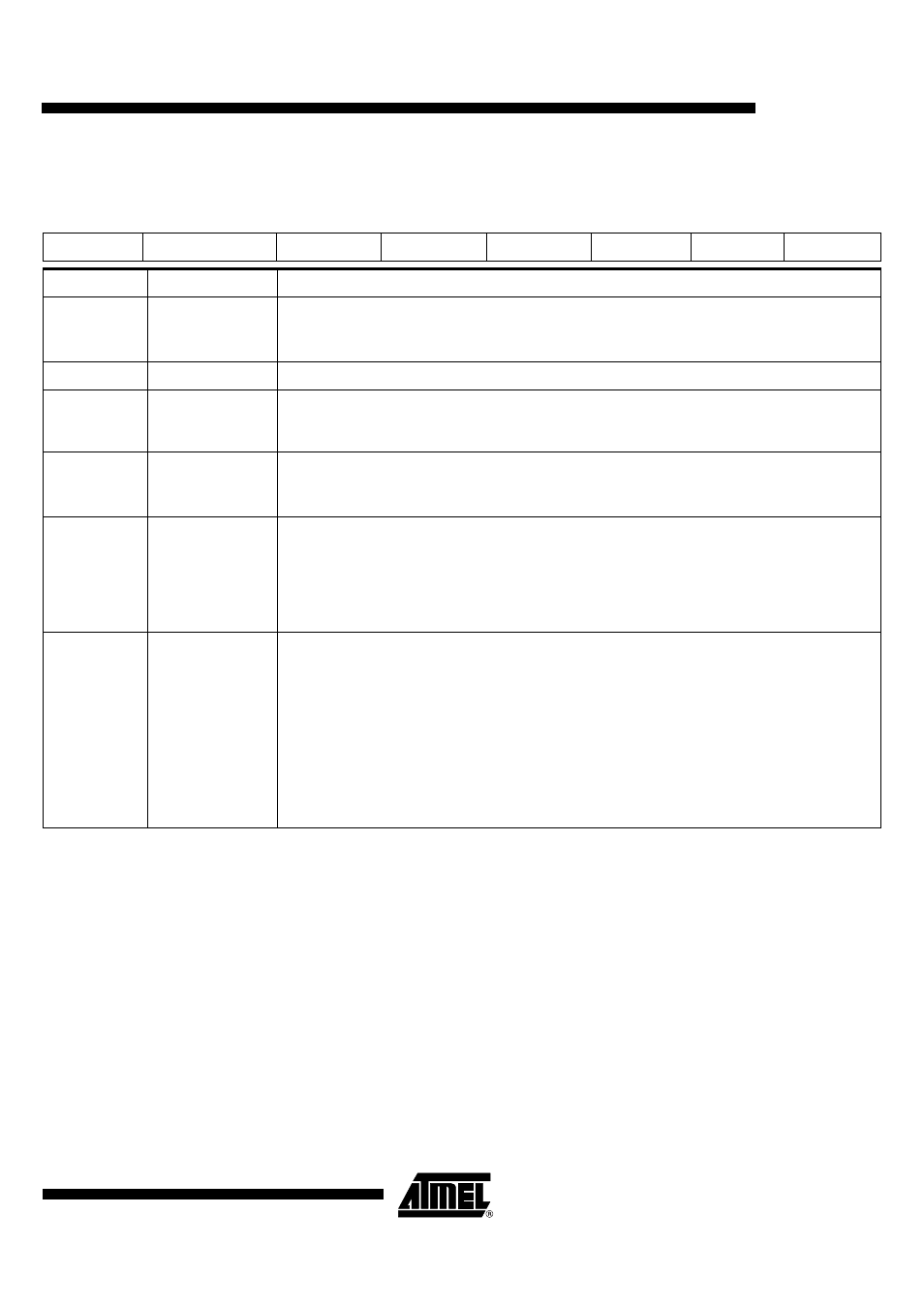

Table 32. SC5_CFG2 ()

7

6

5

4

3

2

1

0

ART5

X

CARDRST5

CARDCK5

CKSTOP5

CKS52

CKS51

CKS50

Bit Number

Bit Mnemonic

Description

7

ART5

Automatic Reset Transition

Set this bit to have the CRST5 pin changed according to activation sequence.

Clear this bit to have the CRST5 pin immediately following the value programmed in CARDRST5.

6

X

5

CARDRST5

Card Reset

Set this bit to enter a reset sequence according to ART5 bit value.

Clear this bit to drive a low level on the CRST5 pin.

4

CARDCK5

Card Clock

Set this bit to set a high level on the CCLK5 pin (according to CKSTOP5 bit value).

Clear this bit to drive a low level on the CCLK5 pin.

3

CKSTOP5

CARD Clock Stop

Set this bit to stop CCLK5 according to CARDCK5. This can be used to set asynchronous cards in power-

down mode (GSM) or to drive CCLK5 by software.

Clear this bit to have CCLK5 running according to CKS5. This can be used to activate asynchronous cards.

Note:

When this bit is changed a special logic ensures that no glitch occurs on the CCLK5 pin and actual

configuration changes can be delayed by half a period to two periods of CCLK5.

2-0

CKS5[2:0]

Interface 5Card Clock Selection

CKS5 [2:0] = 0: CCLK5 = CLK (then the maximum frequency is 24 MHz)

CKS5 [3:0] = 1: CCLK5 = DCCLK

CKS5 [3:0] = 2: CCLK5 = DCCLK / 2

CKS5 [3:0] = 3: CCLK5 = DCCLK / 4

CKS5 [3:0] = 4: CCLK5= A2

CKS5 [3:0] = 5: CCLK5 = A2 / 2

CKS5 [3:0] = 6: CCLK5 = CLK / 2

CKS5 [3:0] = 7: CCLK5 = CLK / 4

The reset value is 0.