At83c26, Slew rate control, Power down mode – Rainbow Electronics AT83C26 User Manual

Page 32

32

7511B–SCR–10/05

AT83C26

After the reading and the clear of the interrupt bits, several bits are used to control the status.

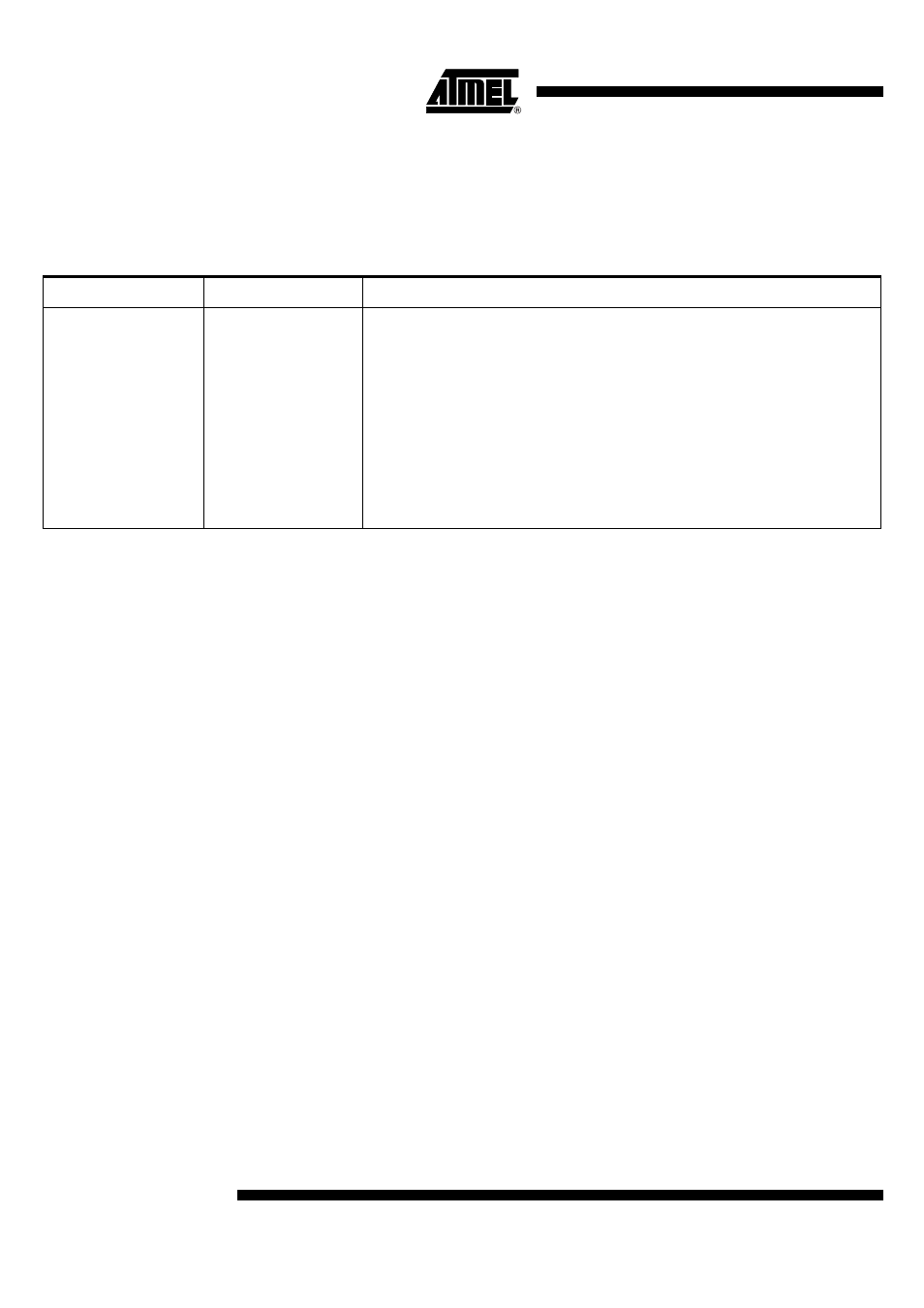

Table 5. Status bits description

The status for the ICARDERR1 and VCARDERRn (n= 1 to 5) bits is controlled with

VCARD_OKn bits.

The status for the ATRERRn (n= 1 to 5) is controlled by reading of values in CAPTURE_MSB

and CAPTURE_LSB.

Slew rate control

The AT83C26 proposed a slew rate control on CIOn and CCLKn pins (n=1, 2, 3, 4, 5). The con-

trol operates on rising and falling edges of CCLKn and only on rising edge of CIOn.

Four modes are available:

•

Automatic mode: The slew rate depends on VCARDn[1:0] value. The slew rate value is

optimized according to CVCCn.

•

Mode 1, 2 , 3 (1.8V, 3V, 5V): The user can forced the slew rate if needed. For example if

CVCCn = 5V, the user can program 1.8V or 3V to speed up the slew rate in case of long wire

connection between AT83C26 and smart cards.

Power down mode

SHUTDOWNA bit and SHUTDOWNB bit must be set to activate power down mode on DCDCA

and DCDCB converters.

If SHUTDOWNA = SHUTDOWNB = 1, the AT83C26 internal regulator also enters in power

down mode. The consumption is then about 30µA.

To exit from power down mode, TWI commands are needed to clear SHUTDOWNA and

SHUTDOWNB.

Bit name

Register name

Remark

CARDIN1

CARDIN2

VCARD_OK1

VCARD_OK2

VCARD_OK3

VCARD_OK4

VCARD_OK5

VDCB_OK

SC1_STATUS

SC1_STATUS

SC1_STATUS

SC2_CFG0

SC3_CFG0

SC4_CFG0

SC5_CFG0

DCDCB

Smart card presence in SC1

Smart card presence in SC2

CVCC1 voltage in range programmed in VCARD1[1:0]

CVCC2 voltage in range programmed in VCARD2[1:0]

CVCC3 voltage in range programmed in VCARD3[1:0]

CVCC4 voltage in range programmed in VCARD4[1:0]

CVCC5 voltage in range programmed in VCARD5[1:0]

CVCCB voltage in range programmed in VDCB[1:0]