Rainbow Electronics AT86RF401 User Manual

Page 46

46

AT86RF401

1424D–RKE–09/02

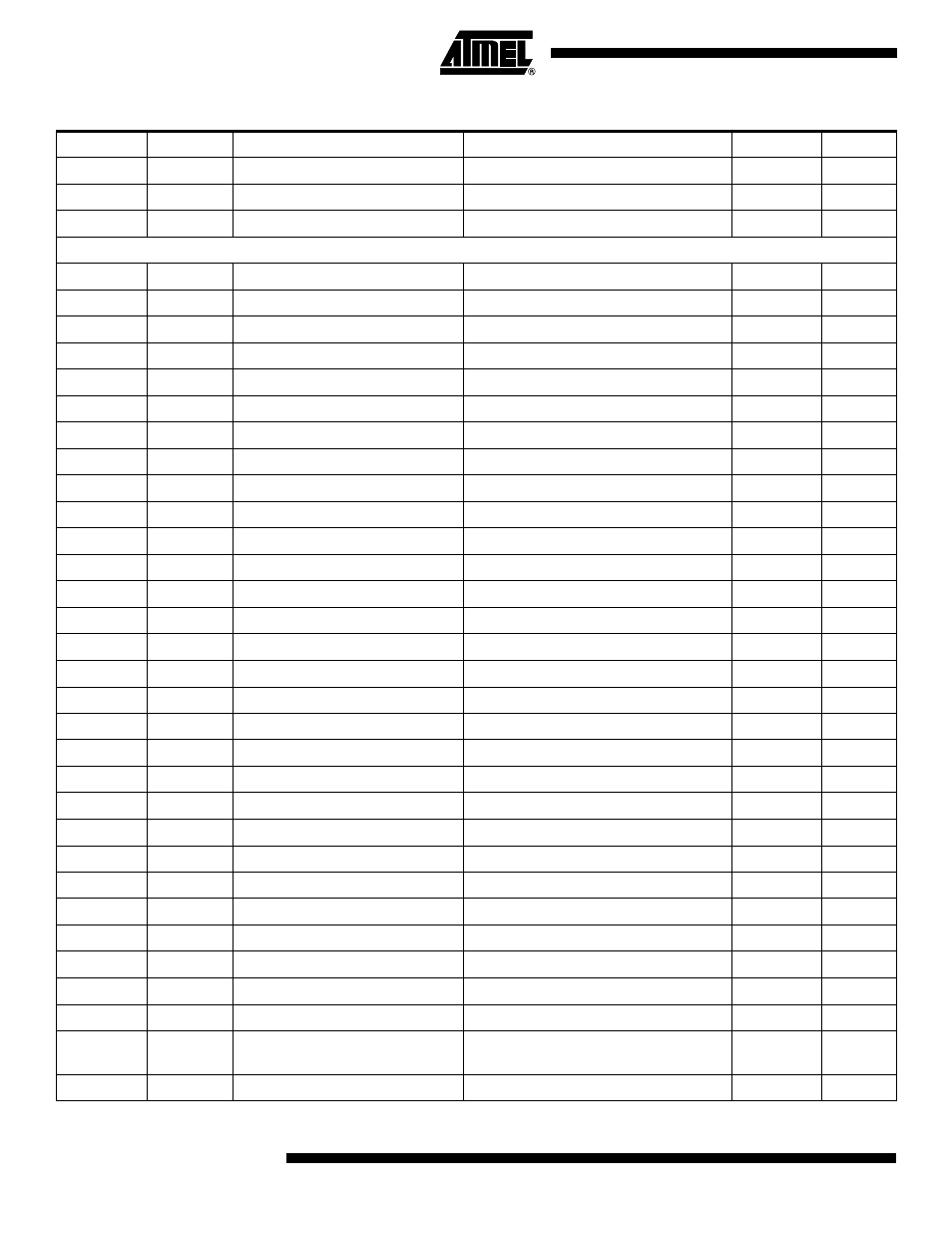

BRVC

k

Branch if Overflow Flag Cleared

If (V = 0) then PC

← PC + k + 1

None

1/2

BRIE

k

Branch if Interrupt Enabled

If (I = 1) then PC

← PC + k + 1

None

1/2

BRID

k

Branch if Interrupt Disabled

If (I = 0) then PC

← PC + k + 1

None

1/2

Data Transfer Instructions

MOV

Rd, Rr

Move Between Registers

Rd

← Rr

None

1

MOVW

Rd, Rr

Copy Register Word

Rd+1:Rd

← Rr + 1:Rr

None

LDI

Rd, K

Load Immediate

Rd

← K

None

1

LD

Rd, X

Load Indirect

Rd

← (X)

None

2

LD

Rd, X+

Load Indirect and Post-Inc.

Rd

← (X), X ← X + 1

None

2

LD

Rd,

−X

Load Indirect and Pre-Dec.

X

← X − 1, Rd ← (X)

None

2

LD

Rd, Y

Load Indirect

Rd

← (Y)

None

2

LD

Rd, Y+

Load Indirect and Post-Inc.

Rd

← (Y), Y ← Y + 1

None

2

LD

Rd,

−Y

Load Indirect and Pre-Dec.

Y

← Y − 1, Rd ← (Y)

None

2

LDD

Rd,Y+q

Load Indirect with Displacement

Rd

← (Y + q)

None

2

LD

Rd, Z

Load Indirect

Rd

← (Z)

None

2

LD

Rd, Z+

Load Indirect and Post-Inc.

Rd

← (Z), Z ← Z + 1

None

2

LD

Rd,

−Z

Load Indirect and Pre-Dec.

Z

← Z − 1, Rd ← (Z)

None

2

LDD

Rd, Z+q

Load Indirect with Displacement

Rd

← (Z + q)

None

2

LDS

Rd, k

Load Direct from SRAM

Rd

← (k)

None

2

ST

X, Rr

Store Indirect

(X)

← Rr

None

2

ST

X+, Rr

Store Indirect and Post-Inc.

(X)

← Rr, X ← X + 1

None

2

ST

− X, Rr

Store Indirect and Pre-Dec.

X

← X − 1, (X) ← Rr

None

2

ST

Y, Rr

Store Indirect

(Y)

← Rr

None

2

ST

Y+, Rr

Store Indirect and Post-Inc.

(Y)

← Rr, Y ← Y + 1

None

2

ST

−Y, Rr

Store Indirect and Pre-Dec.

Y

← Y − 1, (Y) ← Rr

None

2

STD

Y+q,Rr

Store Indirect with Displacement

(Y + q)

← Rr

None

2

ST

Z, Rr

Store Indirect

(Z)

← Rr

None

2

ST

Z+, Rr

Store Indirect and Post-Inc.

(Z)

← Rr, Z ← Z + 1

None

2

ST

−Z, Rr

Store Indirect and Pre-Dec.

Z

← Z − 1, (Z) ← Rr

None

2

STD

Z+q,Rr

Store Indirect with Displacement

(Z + q)

← Rr

None

2

STS

k, Rr

Store Direct to SRAM

(k)

← Rr

None

2

LPM

Load Program Memory

R0

← (Z)

None

3

LPM

Rd, Z

Load Program Memory

Rd

← (Z)

None

3

LPM

Rd, Z+

Load Program Memory and Post-

Inc.

Rd

← (Z), Z ← Z+1

None

3

IN

Rd, P

In Port

Rd

← P

None

1

Table 10. Instruction Set (Continued)

Mnemonics

Operands

Description

Operation

Flags

#Clocks