Rainbow Electronics AT86RF401 User Manual

Page 44

44

AT86RF401

1424D–RKE–09/02

• Bit[4] – S: Sign Bit, S = N

⊕V

The S-bit is always an exclusive or between the negative flag N and the two’s comple-

ment overflow flag V. See Table 10 for detailed information.

• Bit[3] – V: Two’s Complement Overflow Flag

The two’s complement overflow flag V supports two’s complement arithmetics. See

Table 10 below for detailed information.

• Bit[2] – N: Negative Flag

The negative flag N indicates a negative result after the different arithmetic and logic

operations. See Table 10 below for detailed information.

• Bit[1] – Z: Zero Flag

The zero flag Z indicates a zero result after the different arithmetic and logic operations.

See Table 10 below for detailed information.

• Bit[0] – C: Carry Flag

The carry flag C indicates a carry in an arithmetic or logic operation. See Table 10 for

detailed information.

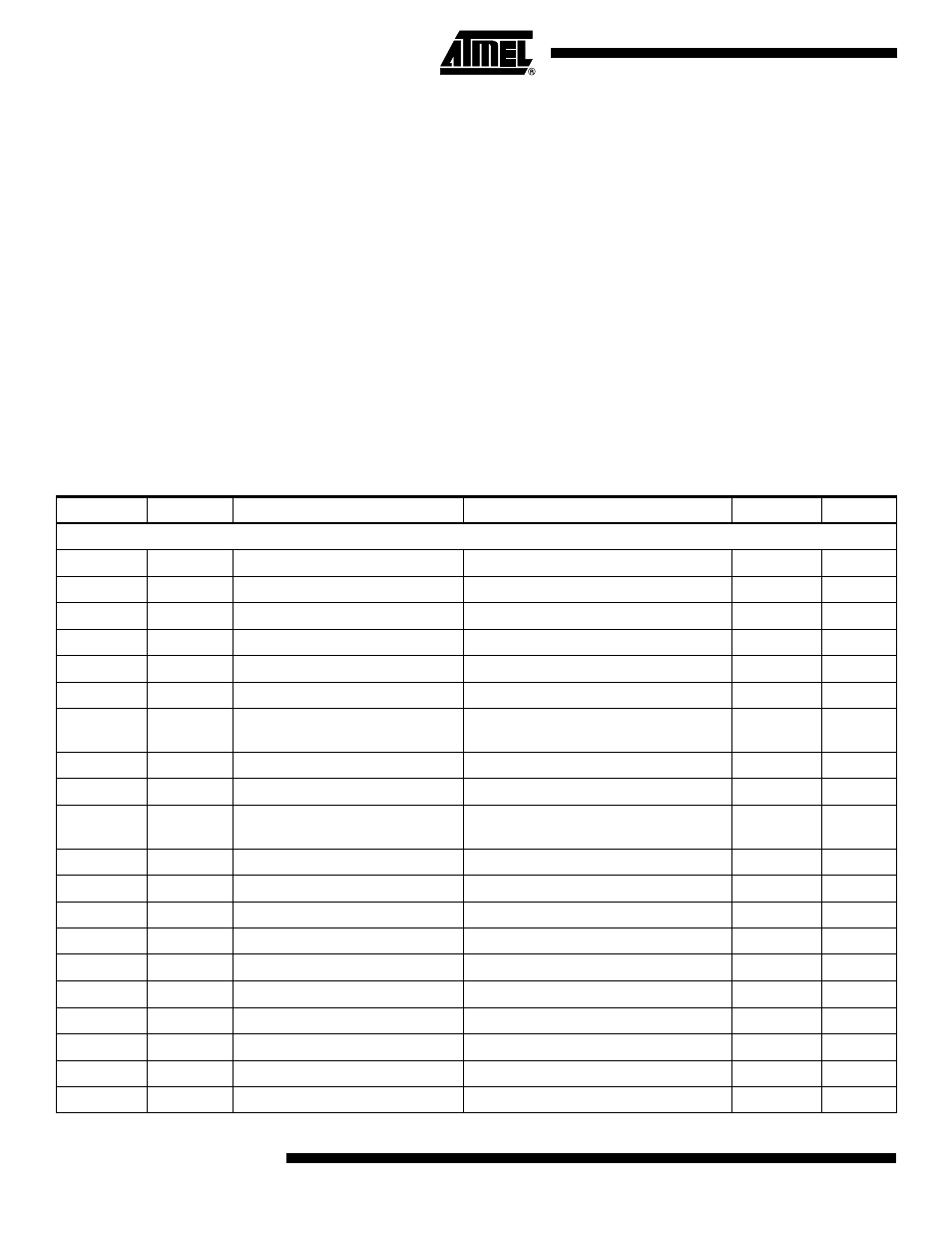

Table 10. Instruction Set

Mnemonics

Operands

Description

Operation

Flags

#Clocks

Arithmetic and Logic Instructions

ADD

Rd, Rr

Add Two Registers

Rd

← Rd + Rr

Z,C,N,V,H

ADC

Rd, Rr

Add with Carry Two Registers

Rd

← Rd + Rr + C

Z,C,N,V,H

1

ADIW

Rdl,K

Add Immediate to Word

Rdh:Rdl

← Rdh:Rdl + K

Z,C,N,V,S

1

SUB

Rd, Rr

Subtract Two Registers

Rd

← Rd - Rr

Z,C,N,V,H

2

SUBI

Rd, K

Subtract Constant from Register

Rd

← Rd - K

Z,C,N,V,H

1

SBC

Rd, Rr

Subtract with Carry Two Registers

Rd

← Rd - Rr - C

Z,C,N,V,H

1

SBCI

Rd, K

Subtract with Carry Constant from

Register

Rd

← Rd - K - C

Z,C,N,V,H

1

SBIW

Rdl,K

Subtract Immediate from Word

Rdh:Rdl

← Rdh:Rdl - K

Z,C,N,V,S

1

AND

Rd, Rr

Logical AND Registers

Rd

← Rd • Rr

Z,N,V

2

ANDI

Rd, K

Logical AND Register and

Constant

Rd

← Rd • K

Z,N,V

1

OR

Rd, Rr

Logical OR Registers

Rd

← Rd v Rr

Z,N,V

1

ORI

Rd, K

Logical OR Register and Constant

Rd

← Rd v K

Z,N,V

1

EOR

Rd, Rr

Exclusive OR Registers

Rd

← Rd ⊕ Rr

Z,N,V

1

COM

Rd

One’s Complement

Rd

← $FF − Rd

Z,C,N,V

1

NEG

Rd

Two’s Complement

Rd

← $00 − Rd

Z,C,N,V,H

1

SBR

Rd,K

Set Bit(s) in Register

Rd

← Rd v K

Z,N,V

1

CBR

Rd,K

Clear Bit(s) in Register

Rd

← Rd • ($FF - K)

Z,N,V

1

INC

Rd

Increment

Rd

← Rd + 1

Z,N,V

1

DEC

Rd

Decrement

Rd

← Rd − 1

Z,N,V

1

TST

Rd

Test for Zero or Minus

Rd

← Rd • Rd

Z,N,V

1