Sram data memory, Program and data addressing modes – Rainbow Electronics AT86RF401 User Manual

Page 21

21

AT86RF401

1424D–RKE–09/02

SRAM Data Memory

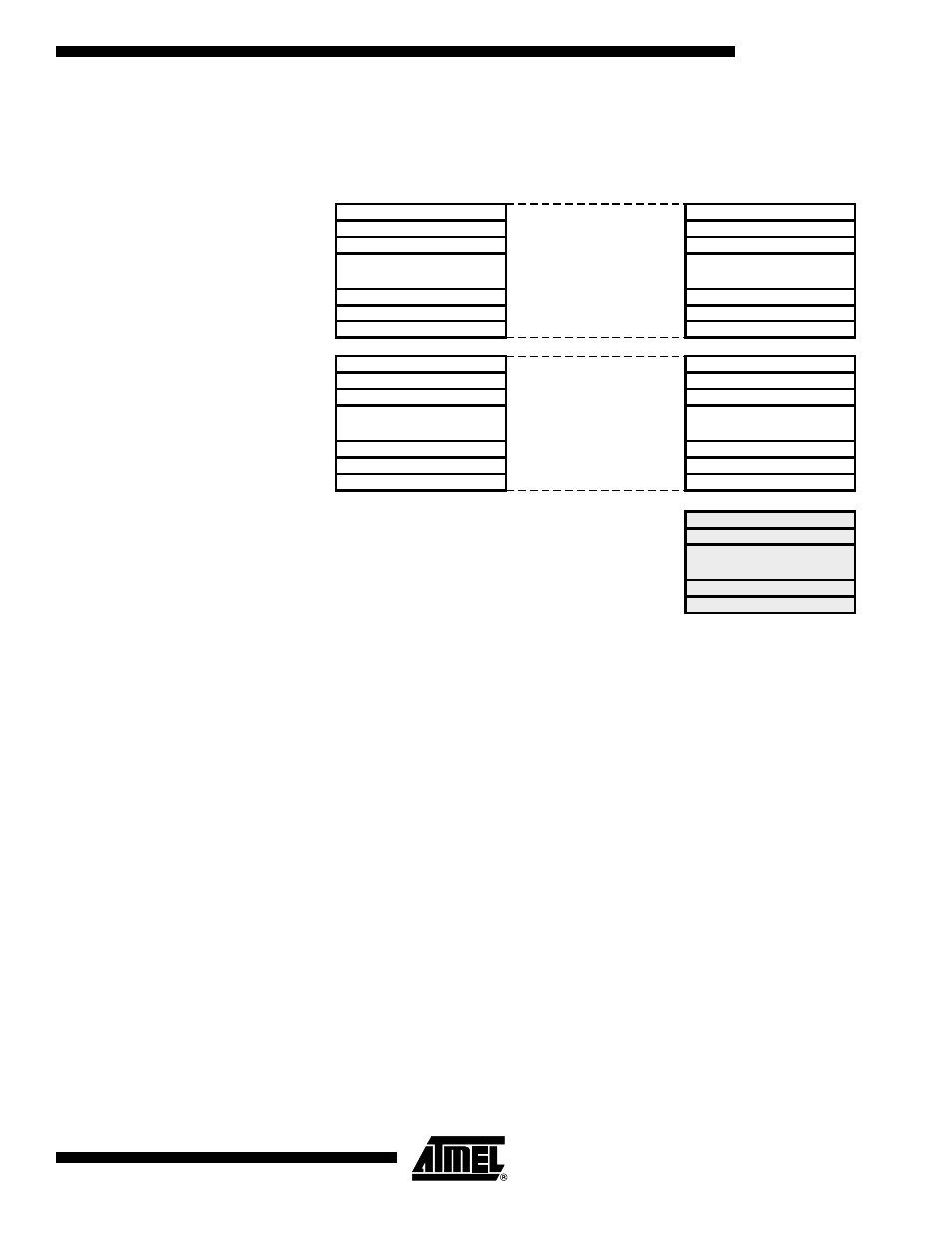

Figure 10 shows how the AT86RF401 SRAM memory is organized.

Figure 10. SRAM Organization

The lower 224 Data Memory locations address the Register File, the I/O Memory and

the internal data SRAM. The first 96 locations address the Register File + I/O Memory,

and the next 128 locations address the internal data SRAM.

The five different addressing modes for the data memory cover: Direct, Indirect with Dis-

placement, Indirect, Indirect with Pre-decrement, and Indirect with Post-increment. In

the register file, registers R26 to R31 feature the indirect addressing pointer registers.

The direct addressing reaches the entire data space.

The Indirect with Displacement mode features a 63 address locations reach from the

base address given by the Y or Z register.

When using register indirect addressing modes with automatic pre-decrement and post-

increment, the address registers X, Y and Z are decremented and incremented.

The 32 general-purpose working registers, 64 I/O registers and the 128 bytes of internal

data SRAM in the AT86RF401 are all accessible through all these addressing modes.

Program and Data

Addressing Modes

The AT86RF401 AVR Enhanced RISC microcontroller supports powerful and efficient

addressing modes for access to the program memory (Flash) and data memory (SRAM,

Register File and I/O Memory). This section describes the different addressing modes

supported by the AVR architecture. In the figures, OP means the operation code part of

the instruction word. To simplify, not all figures show the exact location of the address-

ing bits.

Register File

R0

R1

R2

R29

R30

R31

I/O Registers

$00

$01

$02

...

$3D

$3E

$3F

...

$0000

$0001

$0002

$001D

$001E

$001F

$0020

$0021

$0022

...

$005D

$005E

$005F

...

Data Address Space

$0060

$0061

$00DE

$00DF

...

Internal SRAM