Watchdog timer control register – wdtcr – Rainbow Electronics AT86RF401 User Manual

Page 38

38

AT86RF401

1424D–RKE–09/02

• Bit[2]: Flag2

In transmit mode, this flag indicates the Transmit Done condition that occurs when the

buffer is empty and the counter has counted down to “0”. In receive mode, this flag indi-

cates that an edge has occurred, and the AVR should process the count value in the

BTCR and BTCNT registers. This bit is cleared upon read, e.g., IN R16, BTCR.

• Bit[1]: Data Bit

In transmit mode, this is a one-bit buffer that the AVR writes data to and the bit timer

extracts data from. When the bit timer removes the value from this register, the Flag0 bit

is set, and if enabled, an interrupt (INT2) is generated. If the interrupt is used, the ISR

should load a new bit into the buffer. If the interrupt is not enabled, then a polling method

should be used to detect Flag0 being set. Because of overhead associated with interrupt

handling, it may be slightly faster to use polling.

In receive mode, the value in this register indicates whether the edge at the IO3 pin was

rising or falling. A “1” indicates a rising edge occurred, and a “0” indicates that a falling

edge was detected. The number of AVR clock cycles since the last edge is held in the

C[9:0] (

countval) bits (that is, unless an overflow condition has occurred).

• Bit[0]: Flag0

In transmit mode, this flag indicates the buffer is empty and the AVR should load new

data into it. In receive mode, this indicates a counter overflow condition has occurred.

The AVR should increment its software counter if this condition has occurred. This bit is

cleared upon read, e.g., IN R16, BTCR.

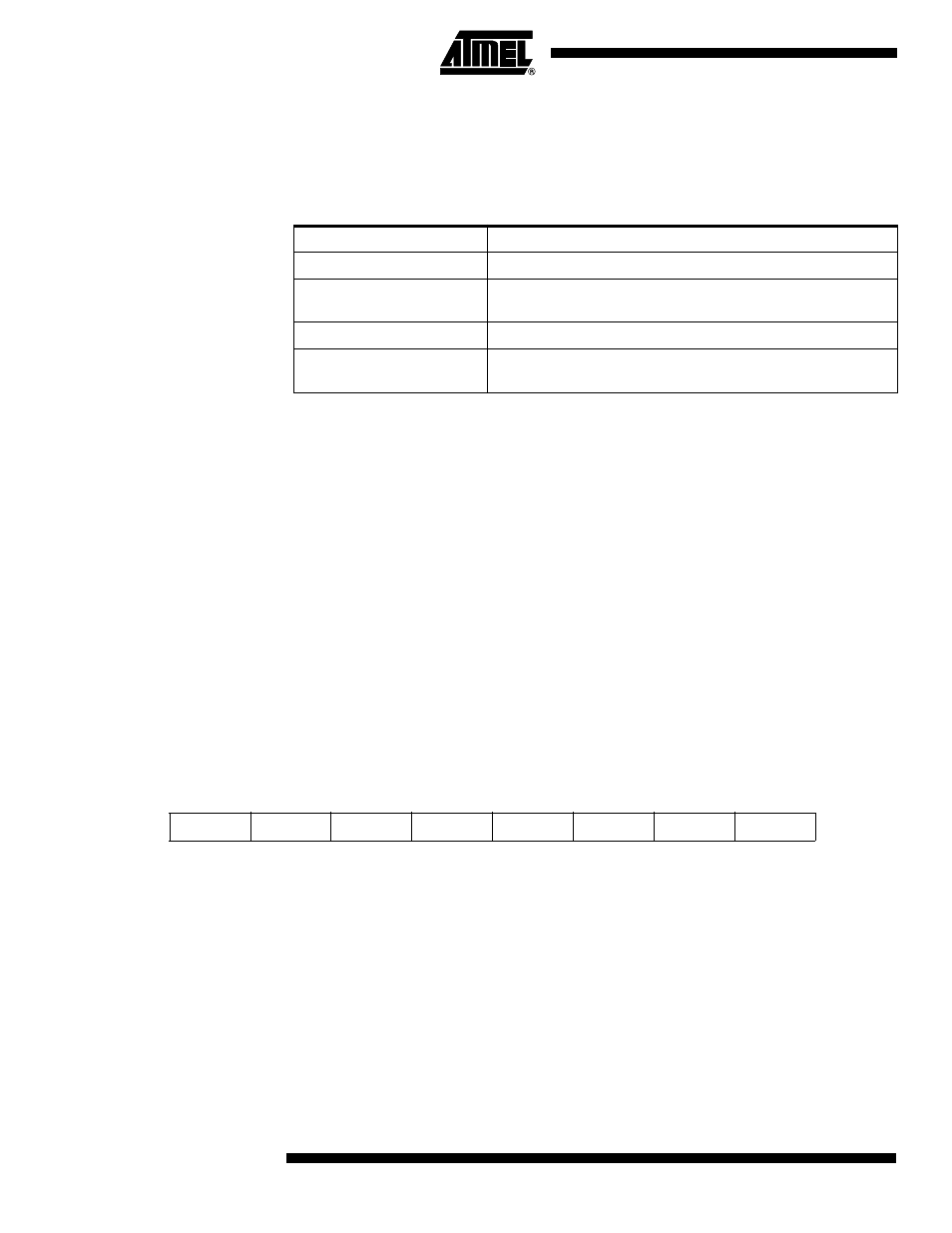

Watchdog Timer Control Register – WDTCR

• Bits[7:5]

Reserved. These bits will always read as “0”.

• Bit[4]: WDTOE, Watchdog Turn-off Enable

This bit must be set (“1”) when the WDE bit is cleared. Otherwise, the watchdog will not

be disabled. Once set, hardware will clear this bit to “0” after four clock cycles. Refer to

the description of the WDE bit for a watchdog disable procedure.

• Bit[3]: WDE, Watchdog Enable

When the WDE is set (“1”), the Watchdog Timer is enabled, and if the WDE is cleared

(“0”), the Watchdog Timer function is disabled. WDE can only be cleared if the WDTOE

Mode[1:0]

Flag2 Function

00

Disabled

01

Indicates Transmit Done condition; buffer is empty and the

counter has expired.

10

An edge has been detected at the IO3 pin.

11

Indicates Transmit Done condition; buffer is empty and the

counter has expired.

Bit

7

6

5

4

3

2

1

0

$22

–

–

–

WDTOE

WDE

WDP2

WDP1

WDP0

WDTCR

Read/Write

R

R

R

R/W

R/W

R/W

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0