Xilinx DS610 User Manual

Page 90

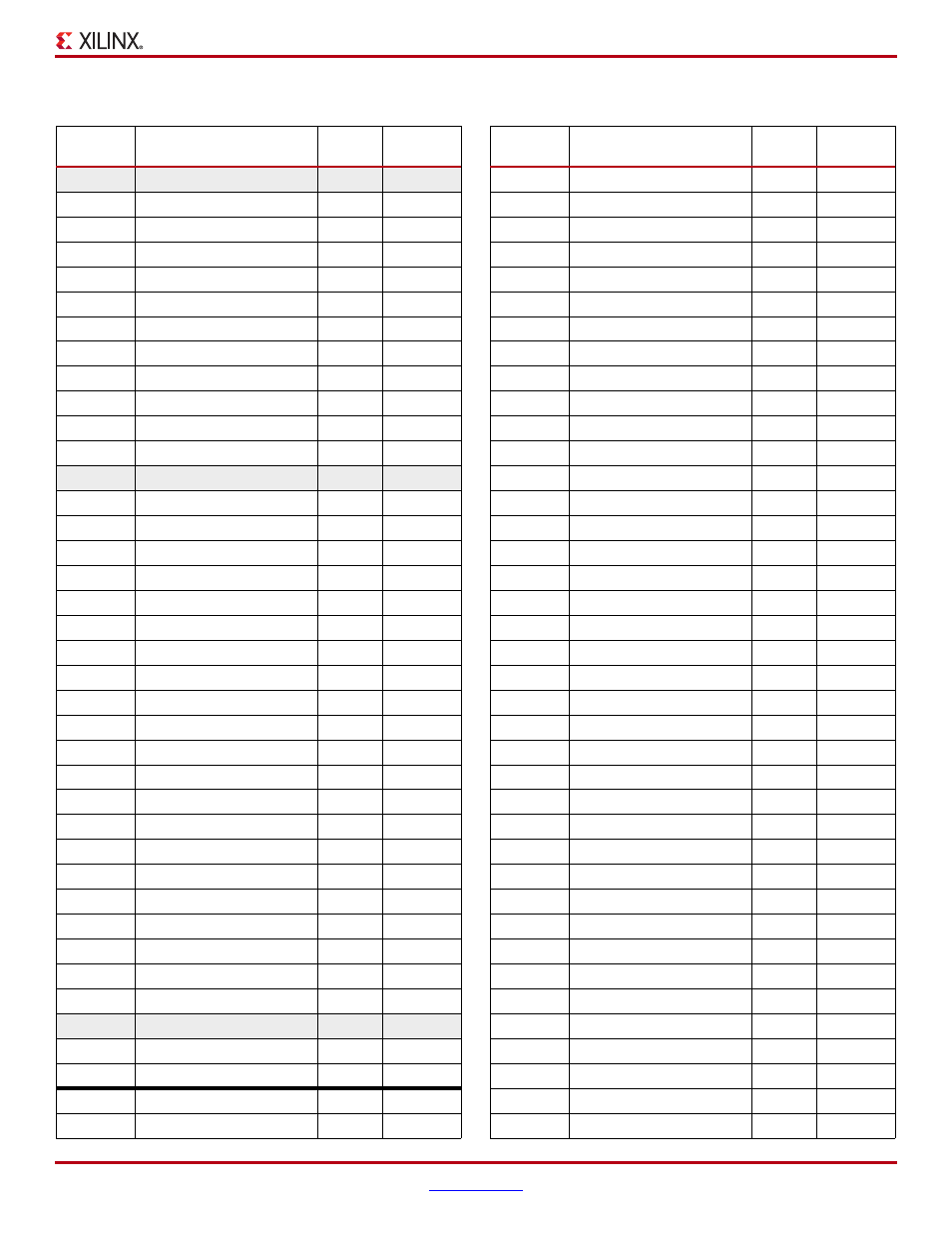

Spartan-3A DSP FPGA Family: Pinout Descriptions

DS610 (v3.0) October 4, 2010

Product Specification

90

1

IP_1/VREF_1

G25

VREF

1

IO_L58P_1/VREF_1

F22

VREF

1

IO_L56N_1

F23

I/O

1

IO_L54N_1

F24

I/O

1

IO_L54P_1

F25

I/O

1

IO_L56P_1

E24

I/O

1

IO_L60P_1

E26

I/O

1

IO_L61N_1

D24

I/O

1

IO_L61P_1

D25

I/O

1

IO_L60N_1

D26

I/O

1

IO_L63N_1/A23

C25

DUAL

1

IO_L63P_1/A22

C26

DUAL

1

IP_1/VREF_1

B26

VREF

1

IO_L02P_1/LDC1

AE26

DUAL

1

IO_L02N_1/LDC0

AD25

DUAL

1

IO_L05P_1

AD26

I/O

1

IO_L03P_1/A0

AC23

DUAL

1

IO_L03N_1/A1

AC24

DUAL

1

IO_L05N_1

AC25

I/O

1

IO_L06P_1

AC26

I/O

1

IO_L07P_1

AB23

I/O

1

IO_L07N_1/VREF_1

AB24

VREF

1

IO_L06N_1

AB26

I/O

1

IO_L09P_1

AA22

I/O

1

IO_L09N_1

AA23

I/O

1

IO_L11P_1

AA24

I/O

1

IO_L11N_1

AA25

I/O

1

VCCO_1

W22

VCCO

1

VCCO_1

T19

VCCO

1

VCCO_1

T25

VCCO

1

VCCO_1

N22

VCCO

1

VCCO_1

L19

VCCO

1

VCCO_1

L25

VCCO

1

VCCO_1

H22

VCCO

1

VCCO_1

H25

VCCO

1

VCCO_1

E25

VCCO

1

VCCO_1

AB25

VCCO

2

IO_L02P_2/M2

Y7

DUAL

2

IO_L05N_2

Y9

I/O

Table 68: Spartan-3A DSP FG676 Pinout for

XC3SD3400A FPGA (Cont’d)

Bank

XC3SD3400A Pin Name

FG676

Ball

Type

2

IO_L12P_2

Y10

I/O

2

IO_L17P_2/RDWR_B

Y12

DUAL

2

IO_L25N_2/GCLK13

Y13

GCLK

2

IO_L27P_2/GCLK0

Y14

GCLK

2

IO_L34N_2/D3

Y15

DUAL

2

IP_2/VREF_2

Y16

VREF

2

IO_L43N_2

Y17

I/O

2

IO_L05P_2

W9

I/O

2

IO_L09N_2

W10

I/O

2

IO_L16N_2

W12

I/O

2

IO_L20N_2

W13

I/O

2

IO_L31N_2

W15

I/O

2

IO_L46P_2

W17

I/O

2

IO_L09P_2

V10

I/O

2

IO_L13P_2

V11

I/O

2

IO_L16P_2

V12

I/O

2

IO_L20P_2

V13

I/O

2

IO_L31P_2

V14

I/O

2

IO_L35P_2

V15

I/O

2

IO_L42P_2

V16

I/O

2

IO_L46N_2

V17

I/O

2

IO_L13N_2

U11

I/O

2

IO_L35N_2

U15

I/O

2

IO_L42N_2

U16

I/O

2

IO_L06N_2

AF3

I/O

2

IO_L07N_2

AF4

I/O

2

IO_L10P_2

AF5

I/O

2

IO_L18N_2

AF8

I/O

2

IO_L19N_2/VS0

AF9

DUAL

2

IO_L22N_2/D6

AF10

DUAL

2

IO_L24P_2/D5

AF12

DUAL

2

IO_L26P_2/GCLK14

AF13

GCLK

2

IO_L28P_2/GCLK2

AF14

GCLK

2

IP_2/VREF_2

AF15

VREF

2

IP_2/VREF_2

AF17

VREF

2

IO_L36P_2/D2

AF18

DUAL

2

IO_L37P_2

AF19

I/O

2

IO_L39P_2

AF20

I/O

2

IP_2/VREF_2

AF22

VREF

Table 68: Spartan-3A DSP FG676 Pinout for

XC3SD3400A FPGA (Cont’d)

Bank

XC3SD3400A Pin Name

FG676

Ball

Type